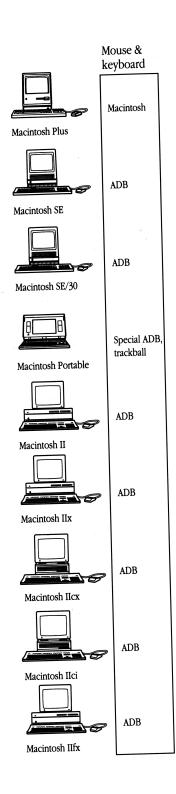

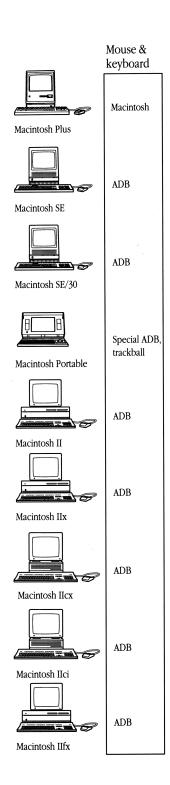

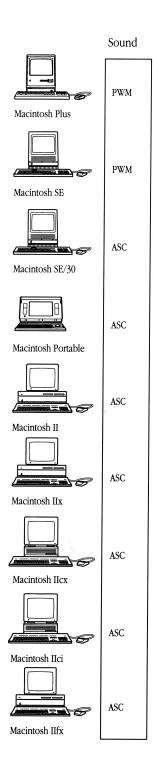

For Macintosh Plus, Macintosh SE, Macintosh SE/30, Macintosh Portable, Macintosh II, Macintosh IIx, Macintosh IIcx, Macintosh IIci, and Macintosh IIfx

# Guide to the Macintosh® Family Hardware

by Apple Computer, Inc.

For Macintosh Plus,

Macintosh SE,

Macintosh SE/30,

Macintosh Portable,

Macintosh II,

Macintosh IIx,

Macintosh IIcx,

Macintosh IIci,

and Macintosh IIfx

# Guide to the Macintosh® Family Hardware

Second Edition

Reading, Massachusetts Menlo Park, California New York Don Mills, Ontario Wokingham, England Amsterdam Bonn Sydney Singapore Tokyo Madrid San Juan

### APPLE COMPUTER, INC.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, mechanical, electronic, photocopying, recording, or otherwise, without prior written permission of Apple Computer, Inc. Printed in the United States of America.

© Apple Computer, Inc., 1990 20525 Mariani Avenue Cupertino, CA 95014-6299 (408) 996-1010

Apple, the Apple logo, Apple IIGS, AppleLink, AppleTalk, A/UX, LaserWriter, Macintosh, and SANE are registered trademarks of Apple Computer, Inc.

APDA, AppleColor, Apple Desktop Bus, FDHD, MPW, QuickDraw, and SuperDrive are trademarks of Apple Computer, Inc.

POSTSCRIPT is a registered trademark, and Illustrator is a trademark, of Adobe Systems Incorporated.

UNIX is a registered trademark of AT&T Information Systems.

PAL is a registered trademark of International Business Machines Corp.

ITC Zapf Dingbats is a registered trademark of International Typeface Corporation.

Microsoft is a registered trademark of Microsoft Corporation.

Motorola is a registered trademark of Motorola, Inc.

Sony is a trademark of Sony Corporation.

NuBus is a trademark of Texas Instruments.

Zilog is a registered trademark of Zilog, Inc.

Simultaneously published in the United States and Canada.

ISBN 0-201-52405-8 3 4 5 6 7 8 9 10-MU-95 94 93 92 91 Third printing, December 1990

Library of Congress Cataloging-in-Publication Data

Guide to the Macintosh Family Hardware. -- 2nd ed. p. cm.

"For Macintosh Plus, Macintosh SE, Macintosh SE/30, Macintosh Portable, Macintosh II, Macintosh IIx, Macintosh IIcx, Macintosh IIci, and Macintosh IIfx."

Prepared by Apple Computer, Inc. ISBN 0-201-52405-8

1. Macintosh (Computer)

I. Apple Computer, Inc. QA76.8.M3G85 1990 621.39'16--dc20 90-34142

#### WARRANTY INFORMATION

ALL IMPLIED WARRANTIES ON THIS MANUAL, INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, ARE LIMITED IN DURATION TO NINETY (90) DAYS FROM THE DATE OF THE ORIGINAL RETAIL PURCHASE OF THIS PRODUCT.

Even though Apple has reviewed this manual, APPLE MAKES NO WARRANTY OR REPRESENTATION, EITHER EXPRESS OR IMPLIED, WITH RESPECT TO THIS MANUAL, ITS QUALITY, ACCURACY, MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE. AS A RESULT, THIS MANUAL IS SOLD "AS IS," AND YOU, THE PURCHASER, ARE ASSUMING THE ENTIRE RISK AS TO ITS QUALITY AND ACCURACY.

IN NO EVENT WILL APPLE BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES RESULTING FROM ANY DEFECT OR INACCURACY IN THIS MANUAL, even if advised of the possibility of such damages.

THE WARRANTY AND REMEDIES SET FORTH ABOVE ARE EXCLUSIVE AND IN LIEU OF ALL OTHERS, ORAL OR WRITTEN, EXPRESS OR IMPLIED. No Apple dealer, agent, or employee is authorized to make any modification, extension, or addition to this warranty.

Some states do not allow the exclusion or limitation of implied warranties or liability for incidental or consequential damages, so the above limitation or exclusion may not apply to you. This warranty gives you specific legal rights, and you may also have other rights which vary from state to state.

# **Contents**

Figures and tables / xv

### Preface About This Book / xxix

What this book contains / xxx

Organization / xxx

Approach / xxxi

Visual cues and conventions / xxxii

Assembly-language variable names / xxxiii

Additional reading / xxxiii

About the Macintosh technical documentation / xxxiv

How to get more information / xxxvi

APDA / xxxvi

User groups / xxxvi

Apple Developer Services / xxxvii

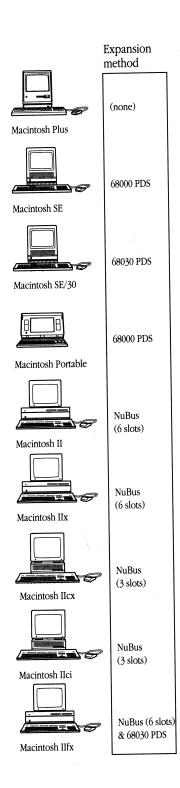

#### 1 Introduction to the Macintosh Hardware / 1

Exterior features of the Macintosh computers / 6

Macintosh 128K, 512K, and 512K enhanced computers / 6

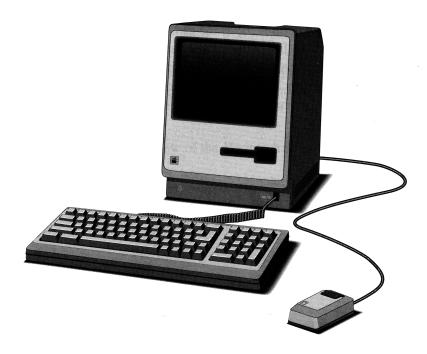

Macintosh Plus computer / 8

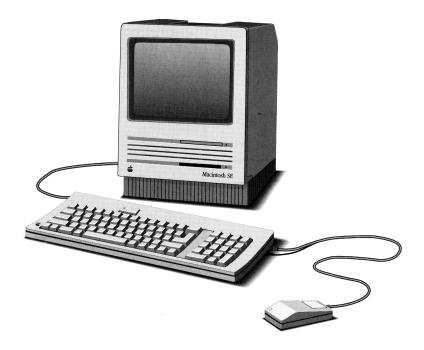

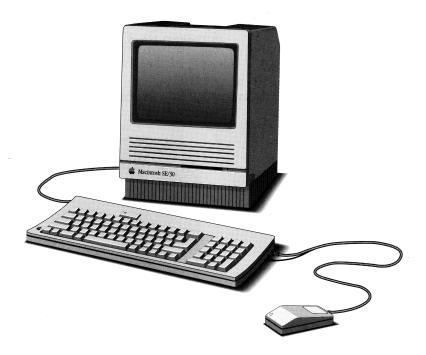

Macintosh SE and Macintosh SE/30 computers / 8

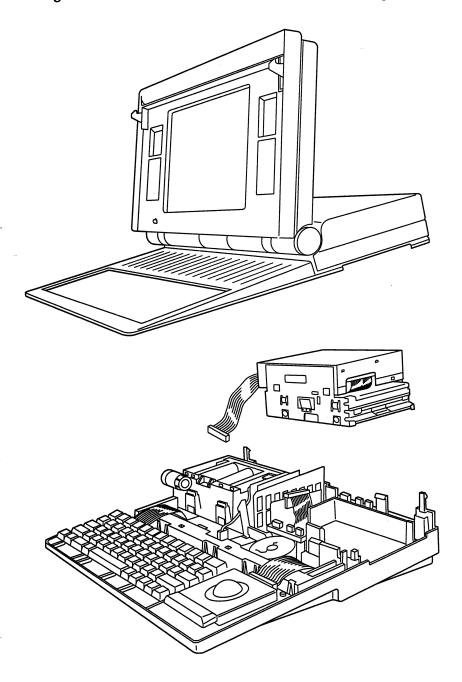

Macintosh Portable computer / 12

Macintosh II–family computers / 13

Inside the Macintosh computers / 18

Classic Macintosh computers / 18

Macintosh SE and Macintosh SE/30 computers / 20

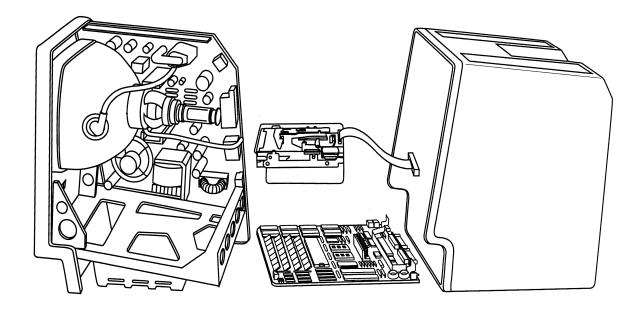

Macintosh SE computer / 20

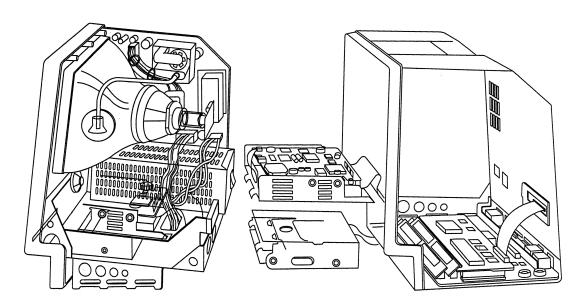

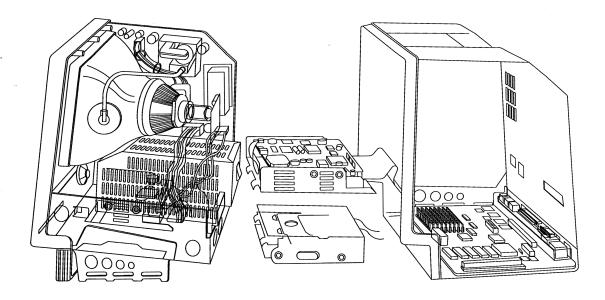

Macintosh SE/30 computer / 22

Macintosh Portable computer / 23

Macintosh II–family computers / 26

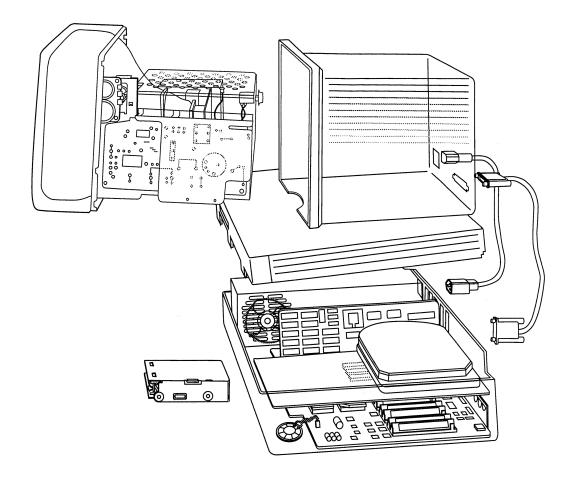

Macintosh II and Macintosh IIx computers / 26

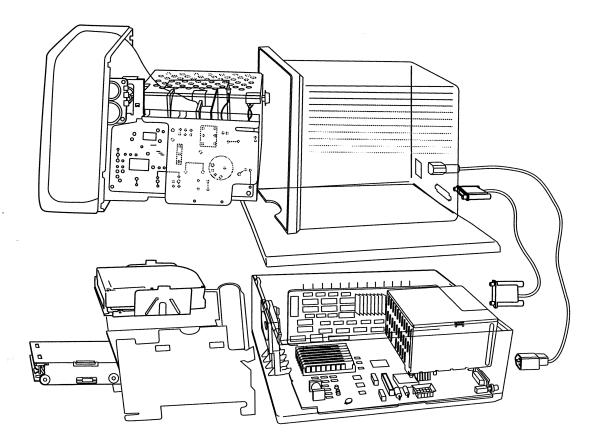

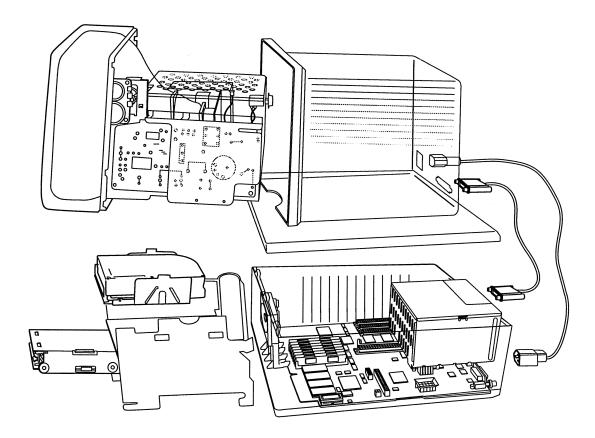

Macintosh IIcx and Macintosh IIci computers / 29 The Macintosh IIfx computer / 32 Memory-mapped device selection / 34 Address maps for 24-bit addresses / 35 Using 32-bit addresses / 40 Address maps for 32-bit addresses / 40 Translating 24-bit addresses to 32-bit addresses / 45 Architecture of the Macintosh Computers / 47 Block diagrams / 49 Compact and portable Macintosh models / 49 Macintosh II family / 55 Data buses / 60 RAM data-bus buffers / 60 Central processing units (CPUs) / 61 Interrupts / 62 Unimplemented instructions / 63 Mathematics coprocessors (FPUs) / 63 Macintosh II memory management unit / 64 Power Manager microprocessor / 64 General logic circuits / 65 RAM / 65 Reading data from RAM / 66 Video RAM / 66 Cache RAM / 67 Cache RAM in the Macintosh IIfx computer / 67 Cache RAM in the Macintosh IIci computer / 68 ROM / 68 Built-in video / 69 Video circuits / 69 Screen-buffer sizes / 70 Sound circuits / 71 Macintosh SE and classic Macintosh sound circuits / 71 Apple Sound Chip / 72 Disk-speed control / 72 VIAs / 73 Non-ADB keyboard interface / 74

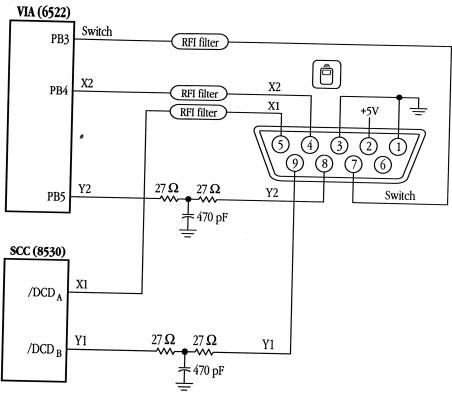

Non-ADB mouse interface / 75

Apple Desktop Bus / 75

```

Real-time clock / 77

SCSI / 78

IWM and SWIM / 80

SCC / 82

I/O Processors / 83

Macintosh expansion interfaces / 83

Processor-direct expansion interfaces / 84

NuBus expansion interfaces / 84

3 Processors and General Logic / 87

Main processor / 89

MC68000 and MC68HC000 microprocessors / 90

Features of the MC68000 / 90

MC68000 interrupts / 91

Interrupts on classic Macintosh computers / 92

Interrupts on the Macintosh SE computer / 93

Interrupts on the Macintosh Portable computer / 95

MC68020 microprocessor / 96

Features of the MC68020 / 96

MC68020 interrupts / 97

MC68030 microprocessor / 100

MC68030 enhancements / 100

MC68030 interrupts / 101

Traps / 103

Auxiliary processors / 104

Memory management units in the Macintosh II computer / 105

Address Management Unit (AMU) / 105

Paged Memory Management Unit (PMMU) / 105

MC68881 and MC68882 mathematics coprocessors / 107

Power Manager IC in the Macintosh Portable computer / 108

IOPs in the Macintosh IIfx computer / 109

IOP interface / 109

IOP for the SCC / 110

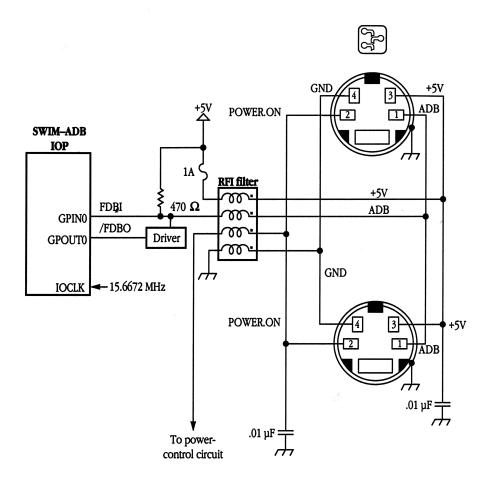

IOP for the SWIM and ADB / 110

General logic circuits / 111

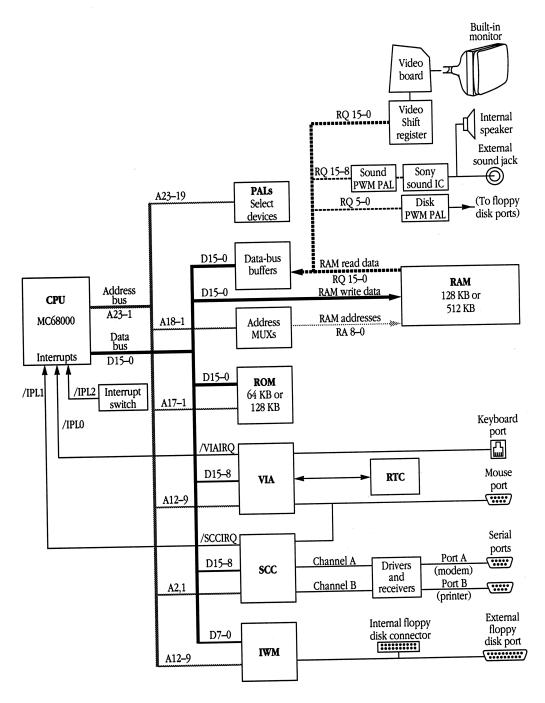

PALs in the classic Macintosh computers / 111

General logic circuits in the Macintosh SE computer / 112

BBU custom IC / 112

GLU custom IC / 113

```

GLUE in the Macintosh SE/30, Macintosh II, and Macintosh IIx computers / 113

Video PALs in the Macintosh SE/30 computer / 114

General logic circuits in the Macintosh IIci computer / 115

Memory Decode Unit (MDU) / 115

MDU functions specific to the Macintosh IIci / 115

MDU functions similar to the GLUE / 115

RAM-Based Video controller (RBV) / 116

RBV functions similar to the GLUE / 116

VIA registers in the RBV / 116

Video functions of the RBV / 117

General logic circuits in the Macintosh Portable computer / 117

CPU GLU custom IC / 118

Miscellaneous GLU custom IC / 118

VDI custom IC / 118

General logic circuits in the Macintosh IIfx computer / 119

Operating System Support (OSS) / 119

Fast Memory Controller (FMC) / 120

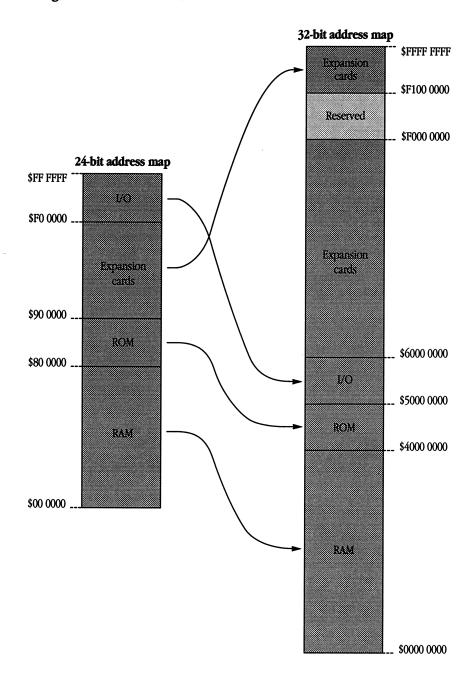

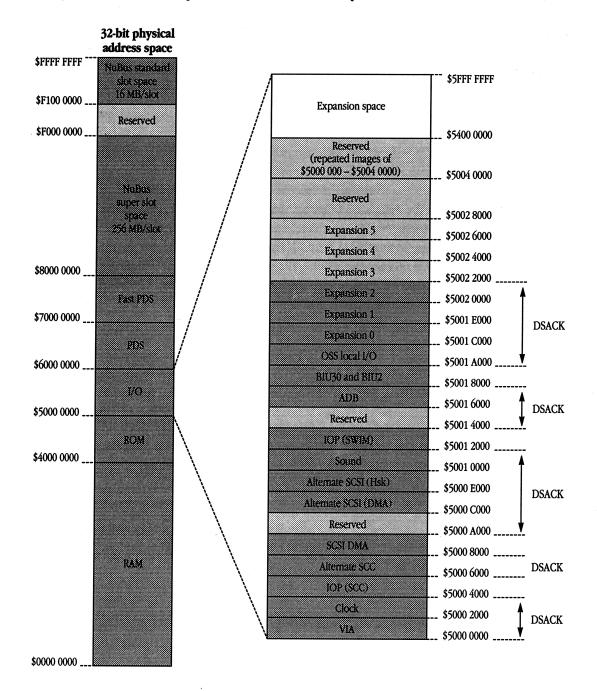

Address maps / 120

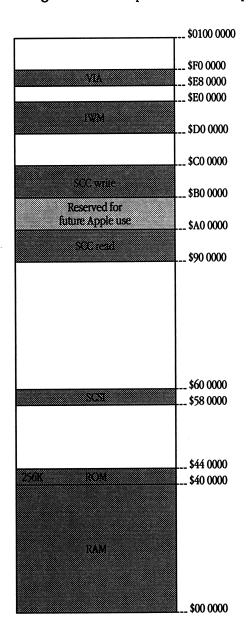

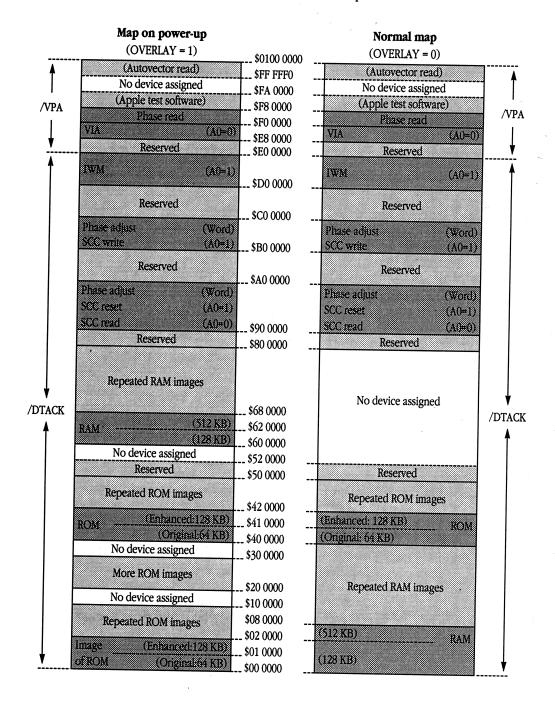

Address map for the classic Macintosh computers / 122

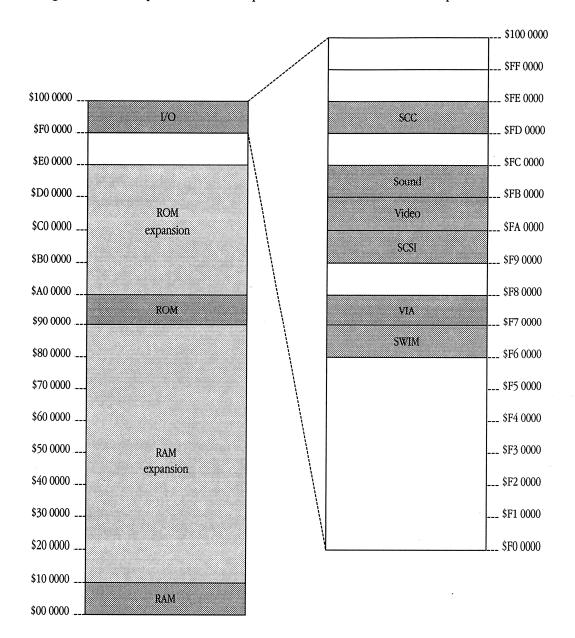

Address map for the Macintosh SE computer / 125

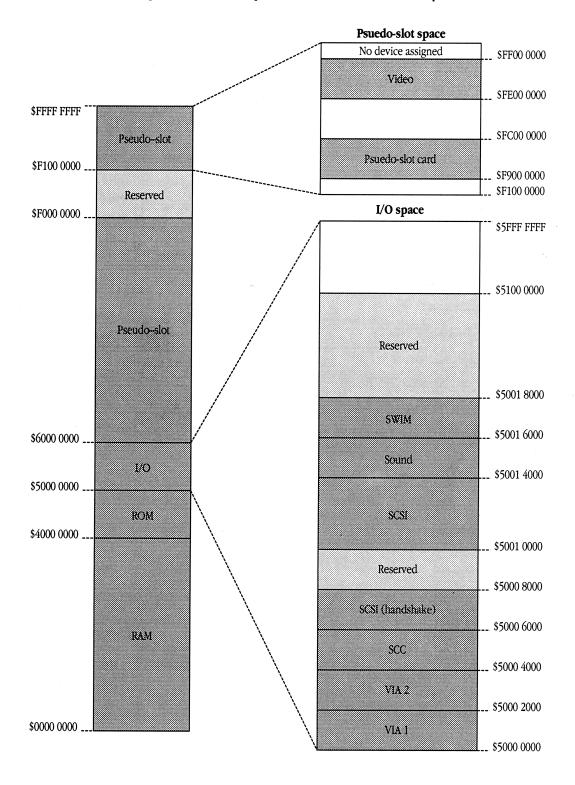

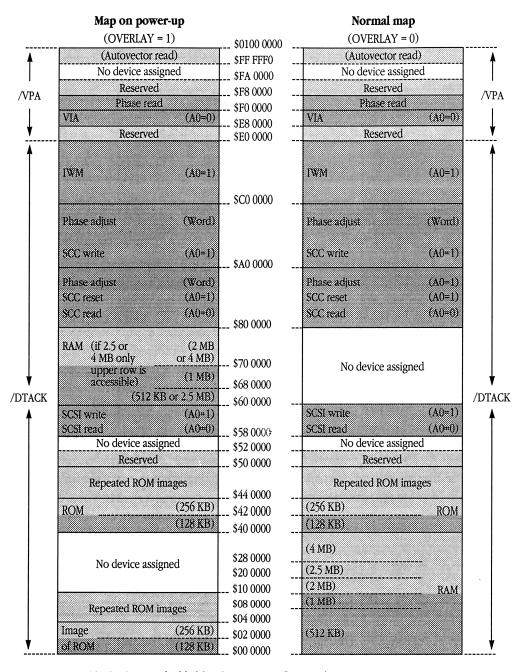

Address map for the Macintosh Portable computer / 128

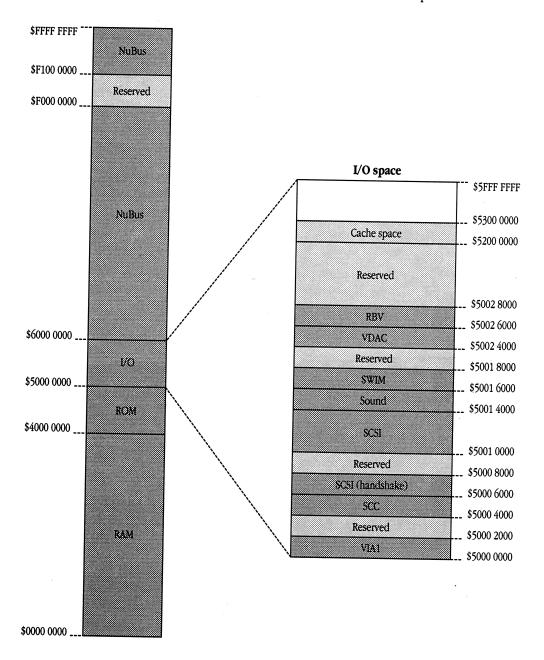

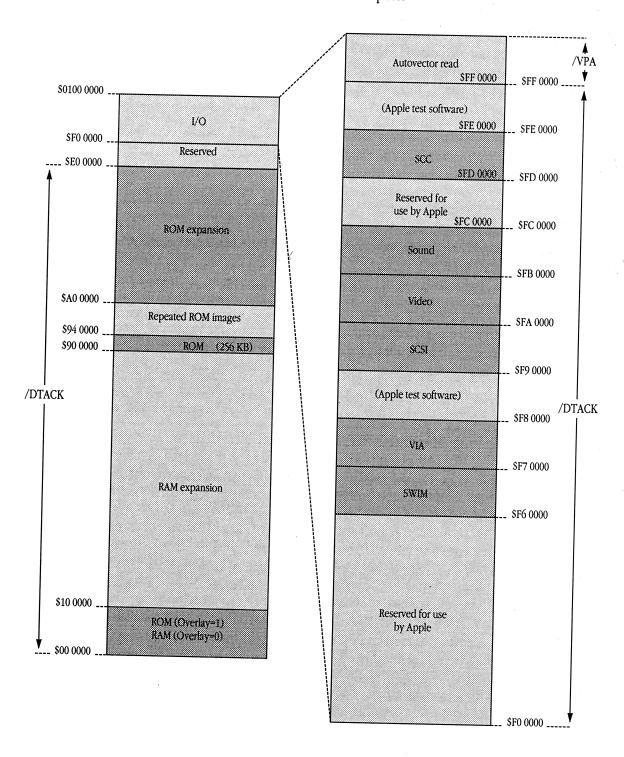

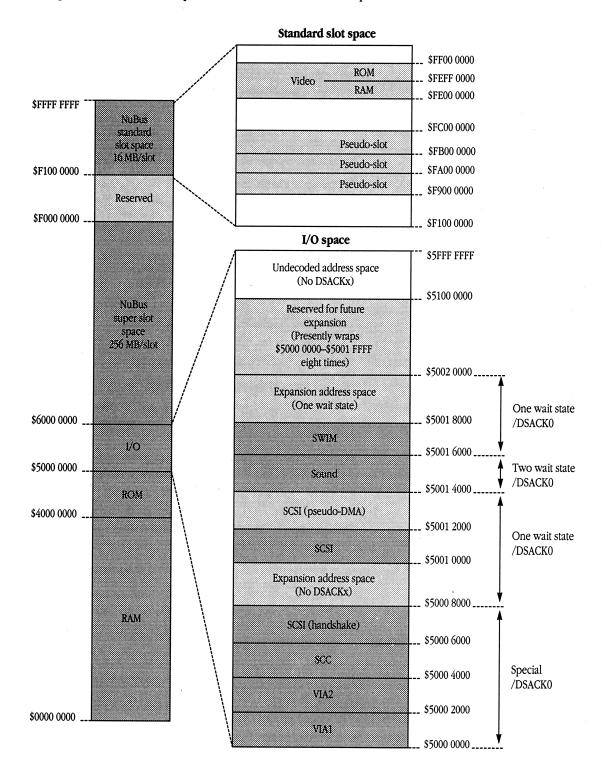

Address map for the Macintosh SE/30 computer / 130

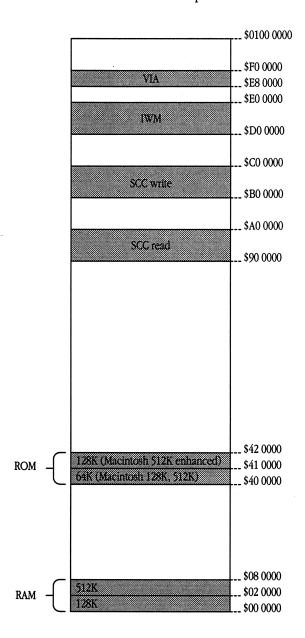

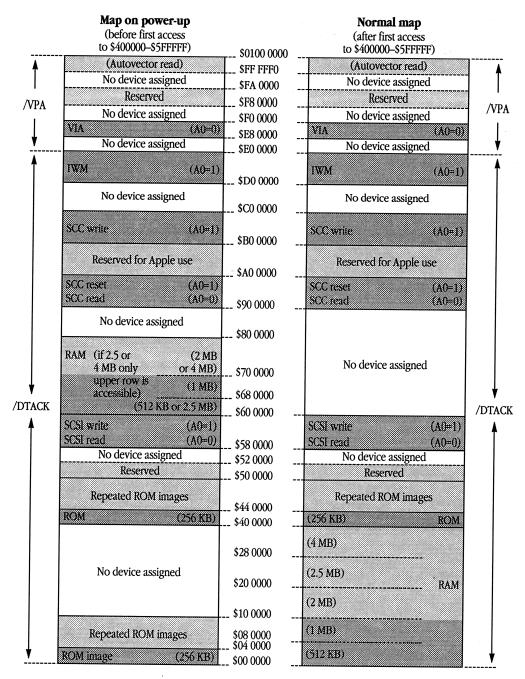

Address map for the Macintosh II, Macintosh IIx, and

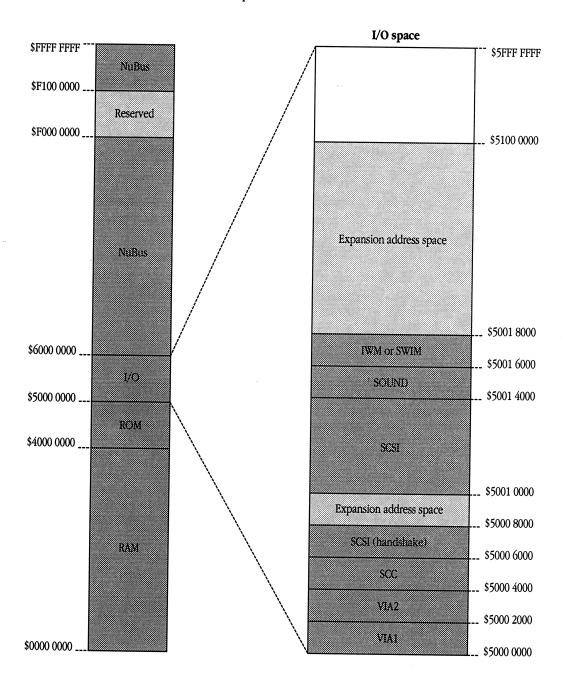

Macintosh IIcx computers / 135

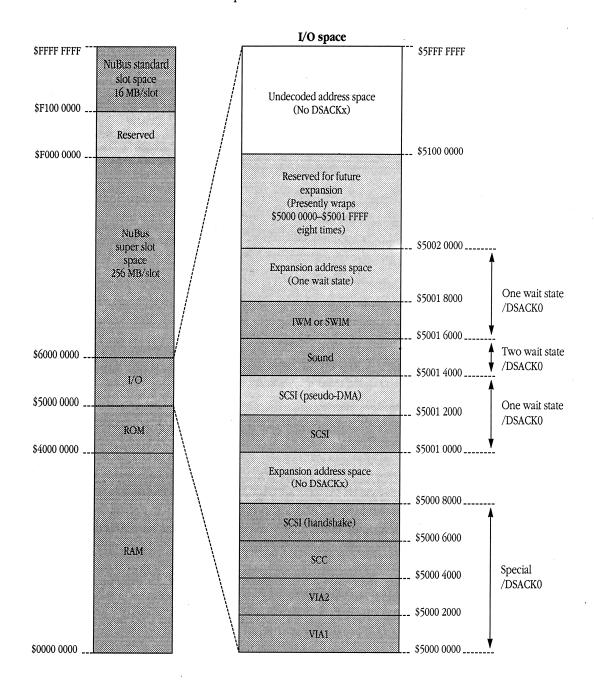

Address map for the Macintosh IIci computer / 141

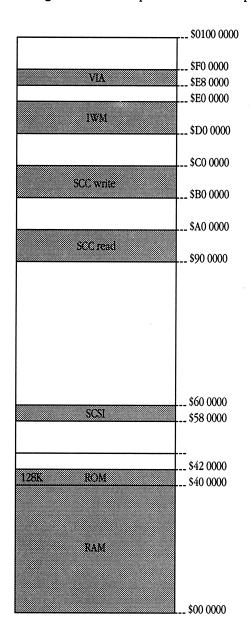

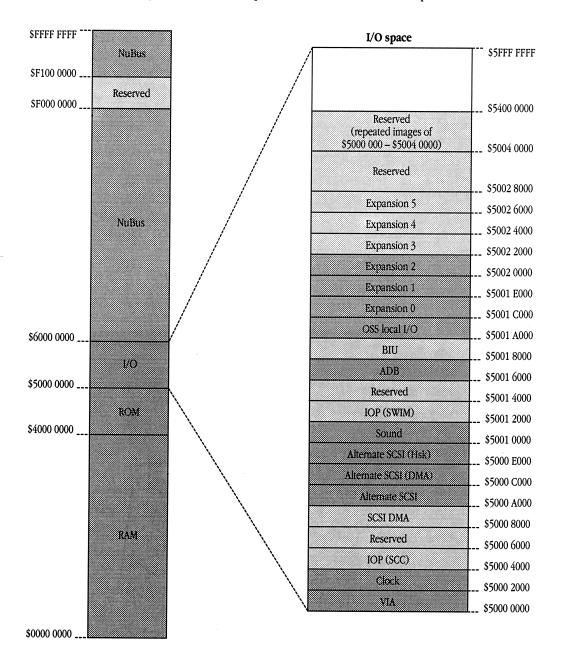

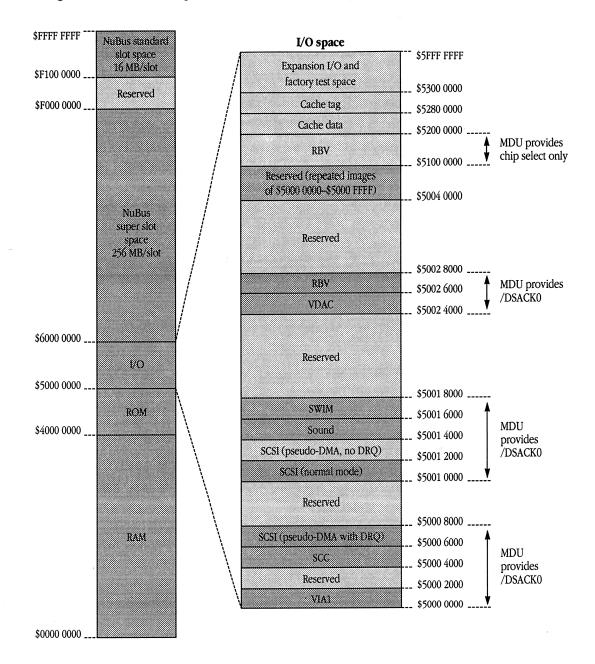

Address map for the Macintosh IIfx computer / 141

Real-time clock (RTC) / 144

Sending commands to the RTC  $\,/\,$  145

The one-second interrupt / 145

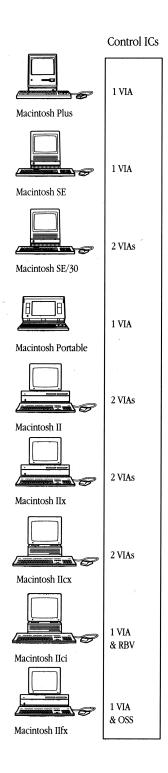

### 4 Versatile Interface Adapter (VIA) ICs / 147

Functions performed by the VIAs  $\,/\,$  150

VIA functions in the classic Macintosh computers / 151

VIA functions in the Macintosh SE computer / 151

VIA functions in the Macintosh Portable computer / 152

VIA functions in the Macintosh SE/30 and Macintosh II-family computers  $/\ 153$

Functions of VIA1 / 153

Functions of VIA1 in the Macintosh II, Macintosh IIx, and Macintosh IIcx computers / 153 Functions of VIA1 in the Macintosh SE/30 computer / 154 Functions of VIA1 in the Macintosh IIci computer / 154 Functions of VIA1 in the Macintosh IIfx computer / 154 VIA1 functions handled by IOPs in the Macintosh IIfx computer / 155 VIA1 functions handled by the OSS in the Macintosh IIfx / 155 Functions of VIA2 / 155 Functions of VIA2 in the Macintosh SE/30, Macintosh II, Macintosh IIx, and Macintosh IIcx computers / 156 VIA2 functions in the Macintosh IIci computer / 157 VIA2 functions in the Macintosh IIfx computer / 157 VIA registers / 158 Data register A / 159 Data register A in machines with only one VIA / 160 VIA Data register A in the classic Macintosh computers / 160 VIA Data register A in the Macintosh SE computer / 161 VIA Data register A in the Macintosh Portable computer / 161 Data register A in VIA1 / 162 VIA1 Data register A in the Macintosh SE/30, Macintosh II, Macintosh IIx, and Macintosh IIcx computers / 162 VIA1 Data register A in the Macintosh IIci computer / 164 VIA1 Data register A in the Macintosh IIfx computer / 164 Data register A in VIA2 / 165 Data register B / 167 Data register B in machines with only one VIA / 167 Data register B in VIA1 / 171 Data register B in VIA2 / 173 Peripheral Control register / 176 Peripheral Control register in VIA1 or VIA / 176 Peripheral Control register in VIA2 / 178 Auxiliary Control register / 179 Shift register / 182 Event timers / 182 Processor-interrupt registers / 183 Interrupt Flag register / 184

Interrupt Enable register / 186

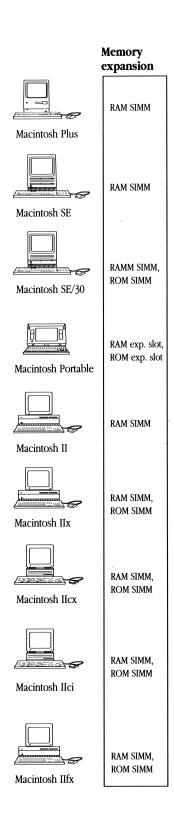

### 5 Memory / 189

RAM / 191

RAM addresses in MC68000-based models / 191

RAM addresses in MC68020-based and MC68030-based models / 192

RAM access cycles / 194

RAM access rate in the Macintosh Plus computer / 194

RAM access rate in the Macintosh SE computer / 195

RAM access rate in the Macintosh Portable computer / 195

RAM access rate in the Macintosh SE/30, Macintosh II,

Macintosh IIx, and Macintosh IIcx computers / 195

RAM access rate in the Macintosh IIci computer / 195

RAM access rate in the Macintosh IIfx computer / 196

RAM configuration in the Macintosh 128K, 512K, and

512K enhanced computers / 196

RAM configuration in the Macintosh Plus and

Macintosh SE computers / 197

RAM configuration in the Macintosh Portable computer / 205

Permanent RAM / 205

Internal expansion RAM / 206

RAM configuration in the Macintosh SE/30 and

Macintosh II-family computers / 209

Video RAM in the Macintosh IIci computer / 221

Parity RAM in the Macintosh IIci computer / 222

Parity RAM in the Macintosh IIfx computer / 222

RAM cache card in the Macintosh IIci computer / 223

Operation of a cache card / 223

Reading with a cache hit / 224

Reading with a cache miss / 224

Writing / 224

Controlling the cache card / 225

Cache card connector / 225

RAM cache in the Macintosh IIfx computer / 228

Operation of the RAM cache / 229

Reading with a cache hit / 229

Reading with a cache miss / 229

Filling the cache / 230

Writing / 230

Buffered write operations in the Macintosh IIfx computer / 230

### ROM / 231

ROM configurations / 232 ROM expansion in the Macintosh Portable computer / 233 ROM SIMMs / 235

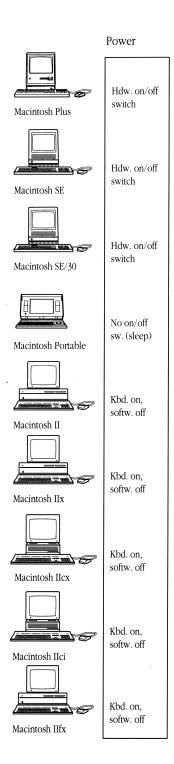

### 6 Power Supplies / 239

Power up, system startup, and power down / 241

Classic Macintosh computers / 242

Macintosh SE computer / 242

Macintosh Portable computer / 243

Macintosh SE/30 and Macintosh II-family computers / 243

Power up / 244

System startup / 244

Macintosh II–family power down / 245

Power connectors / 246

Power input requirements / 252

Macintosh Plus computer / 252

Macintosh SE and Macintosh SE/30 computers / 253

Macintosh Portable computer / 254

Macintosh IIcx and Macintosh IIci computers / 255

Macintosh II, Macintosh IIx, and Macintosh IIfx computers / 256

DC output specifications / 257

Macintosh Plus computer / 257

Macintosh SE and Macintosh SE/30 computers / 259

Macintosh Portable computer / 260

Macintosh IIcx and Macintosh IIci computers / 261

Macintosh II, Macintosh IIx, and Macintosh IIfx computers / 263

Monitor power receptacle in the Macintosh II–family computers  $/\ 264$  Responses to abnormal conditions  $/\ 265$

Power circuit in the Macintosh Portable computer / 266

Battery charger and voltage control circuits / 266

Battery monitor and battery charging circuit / 267

Sleep state in the Macintosh Portable computer / 268

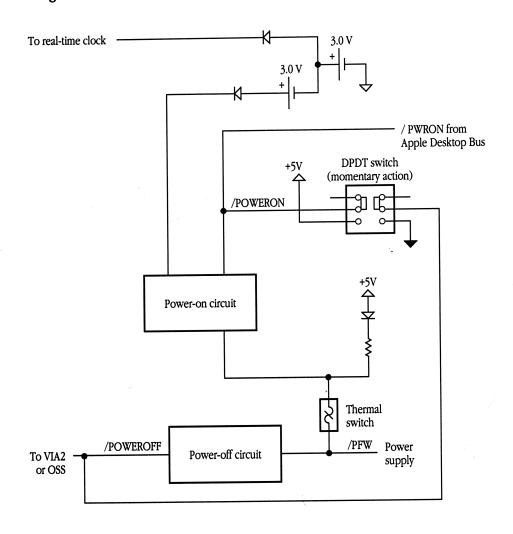

Power-control circuit in the Macintosh II-family computers / 269

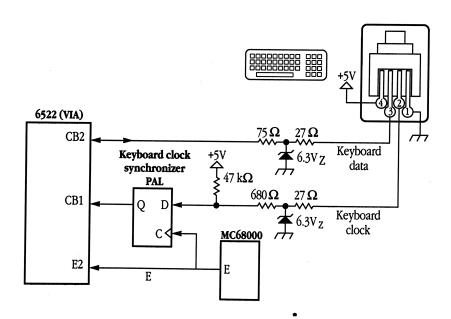

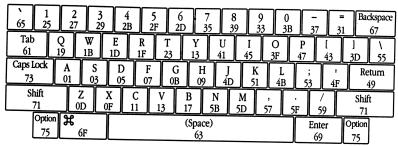

### 7 Macintosh Plus Mouse and Keyboard / 273

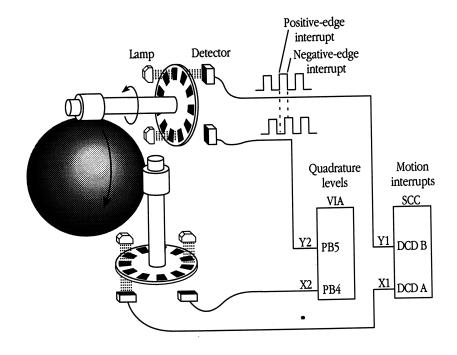

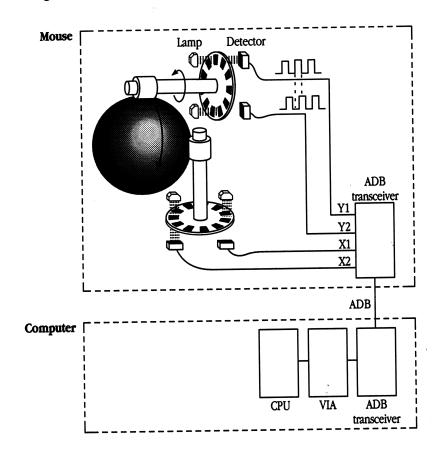

Macintosh Plus mouse / 275

Macintosh Plus mouse mechanism / 275

Macintosh Plus mouse interface / 278

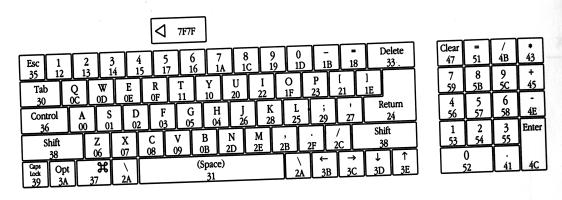

Macintosh Plus keyboard / 280

The Macintosh Plus keyboard interface / 280

Macintosh Plus keyboard communication / 282

Macintosh Plus keyboard and keypad protocol / 283

Earlier keyboard and separate keypad / 284

Communication protocol for the separate keypad / 286

### 8 Apple Desktop Bus / 287

Overview / 289

ADB interface / 291

ADB interface circuits / 292

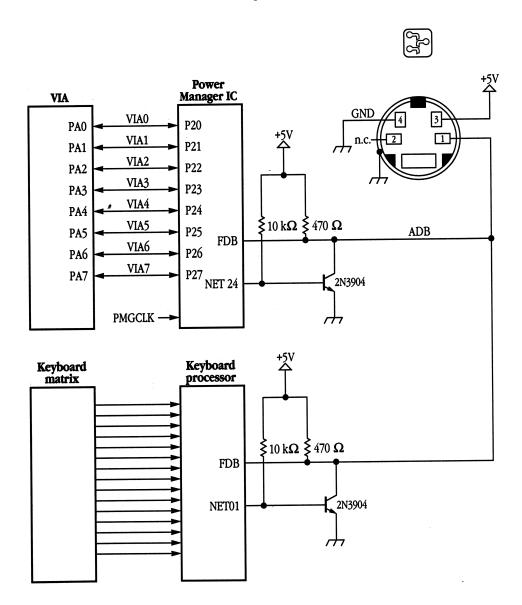

ADB interface circuits on the Macintosh Portable / 296

Macintosh Portable Power Manager IC as ADB controller / 296

Macintosh Portable keyboard processor / 296

Macintosh Portable keyboard and trackball connectors / 297

ADB keyboards and mouse / 300

Apple Standard Mouse / 300

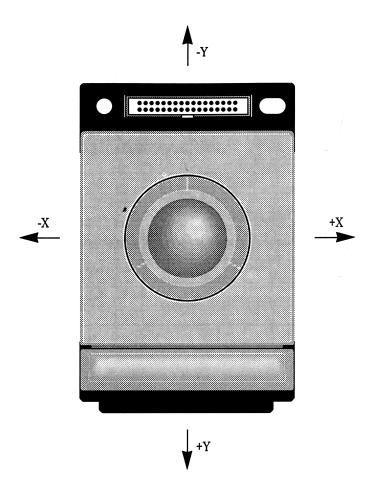

Macintosh Portable low-power trackball / 303

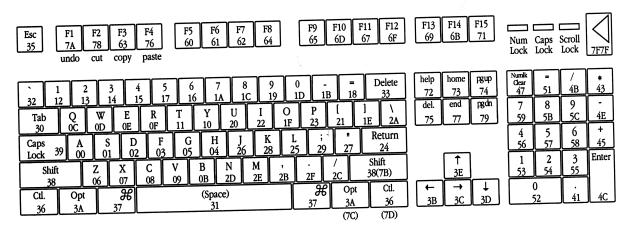

Apple Standard Keyboard / 305

Apple Extended Keyboard / 308

Macintosh Portable low-power keyboard / 310

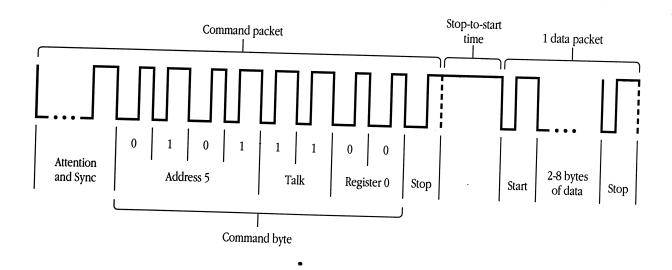

ADB communications / 312

ADB transactions / 313

ADB commands / 315

Talk command / 316

Listen command / 316

SendReset command / 316

Flush command / 316

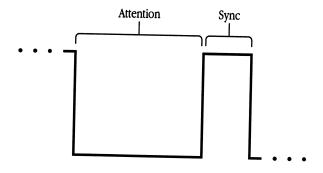

ADB signals / 317

Attention and Sync signals / 317

Global Reset signal / 317

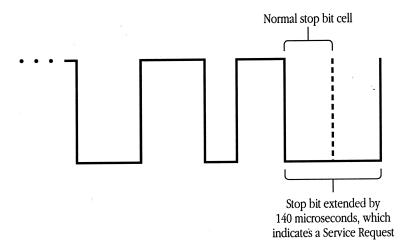

Service Request signal / 318

ADB timing / 319

ADB error conditions / 320

```

ADB peripheral devices / 320

ADB device registers / 320

Register 0 / 321

Register 1 / 321

Register 2 / 321

Register 3 / 321

ADB device addresses / 322

ADB Device Handler ID / 323

ADB collision detection / 324

ADB polling protocol / 325

Controlling the ADB Service Request / 326

```

### Floppy Disk Interfaces / 327

```

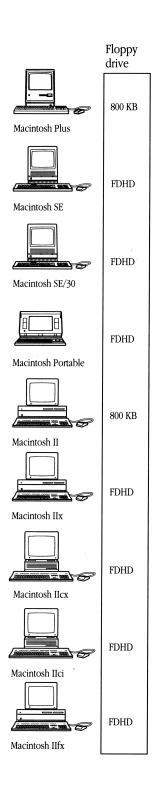

The two types of disk drives / 329

Basic features of the disk drives / 330

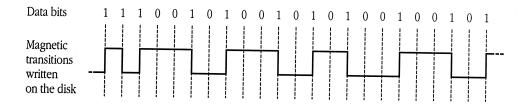

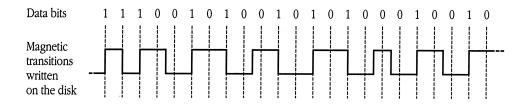

Data encoding methods / 330

Group-code recording (GCR) / 331

Modified frequency modulation (MFM) / 331

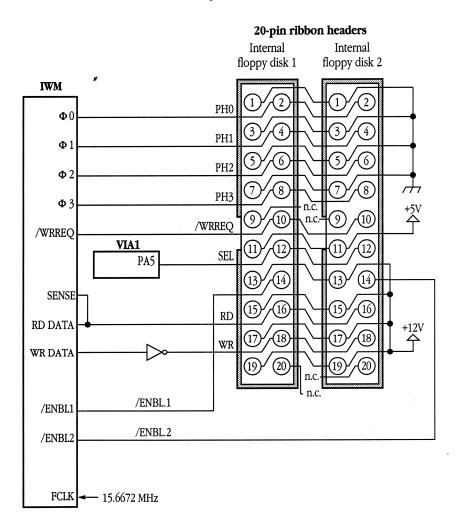

800 KB drive interface / 332

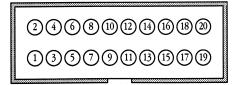

800 KB drive connectors / 334

Internal 800 KB drive connectors / 334

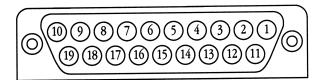

External 800 KB drive connectors / 337

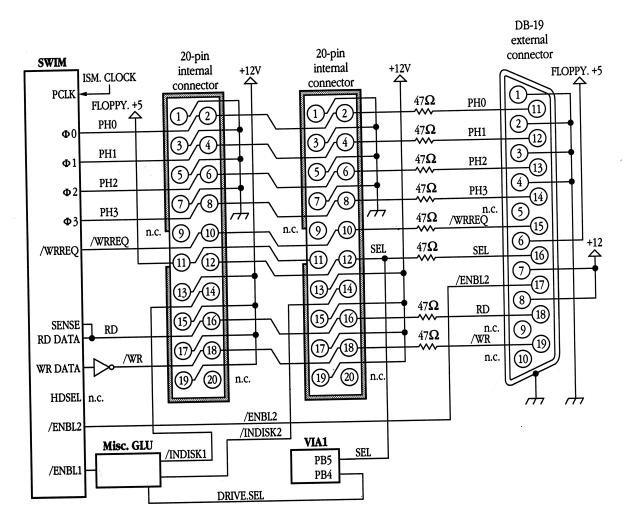

Circuit diagrams for the 800 KB drive interface / 338

Compatibility with single-sided disk drives / 342

Compatibility with the Hard Disk 20 / 342

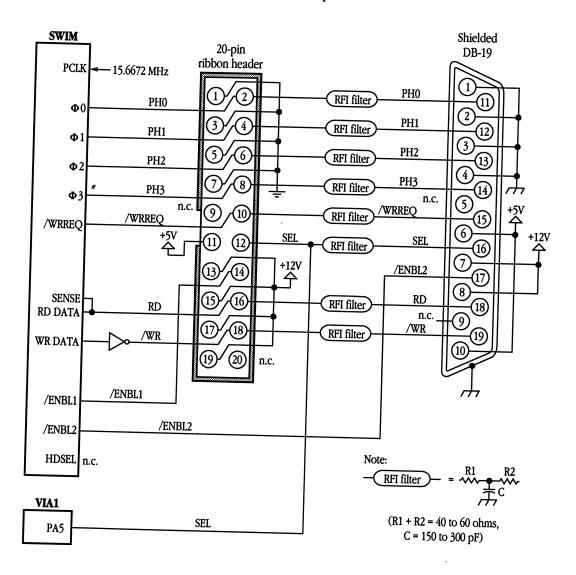

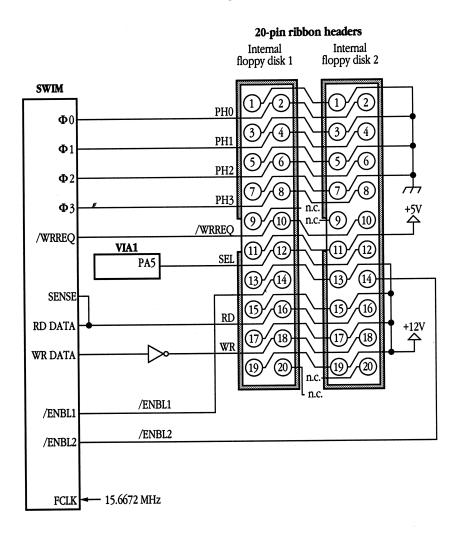

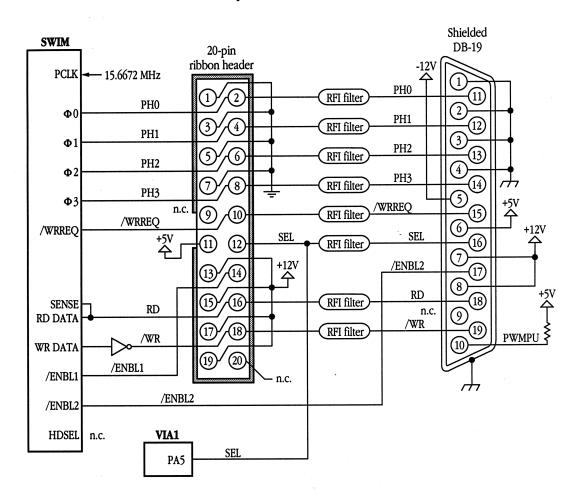

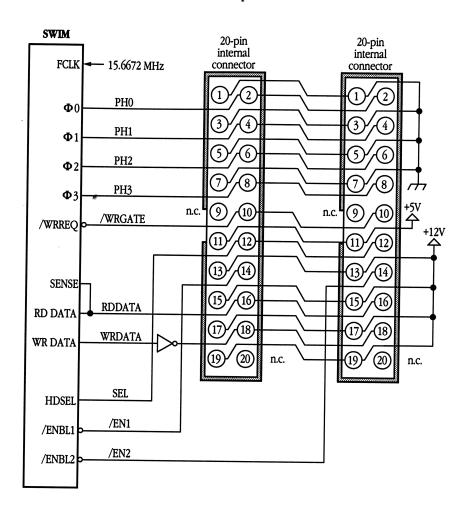

FDHD drive interface / 343

FDHD drive connectors / 345

Internal FDHD drive connectors / 345

External FDHD drive connectors / 348

FDHD interface circuit diagrams / 350

Incompatibility with the single-sided disk drive / 356

Compatibility with the Hard Disk 20 / 356

```

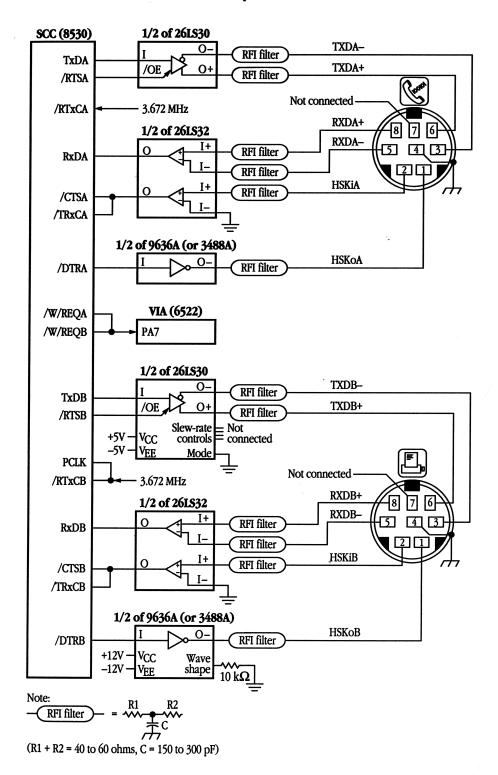

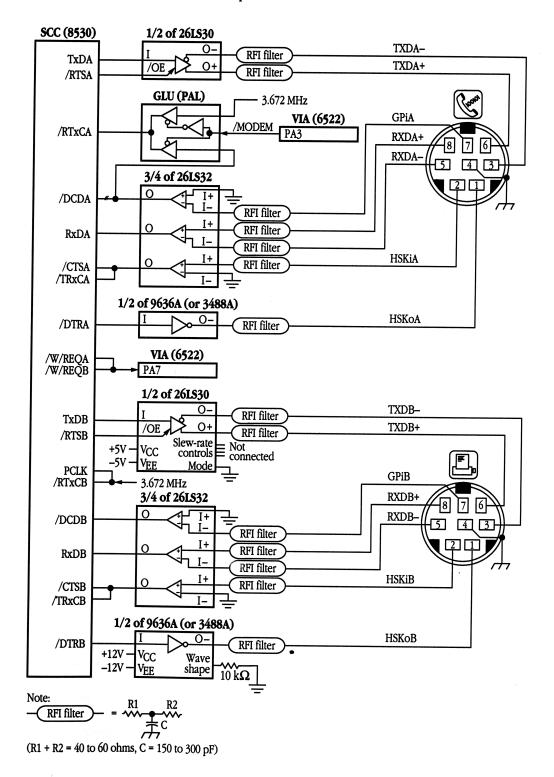

### 10 Serial I/O Ports / 357

Serial port connectors / 359

Signals on the serial ports / 361

SCC addresses / 363

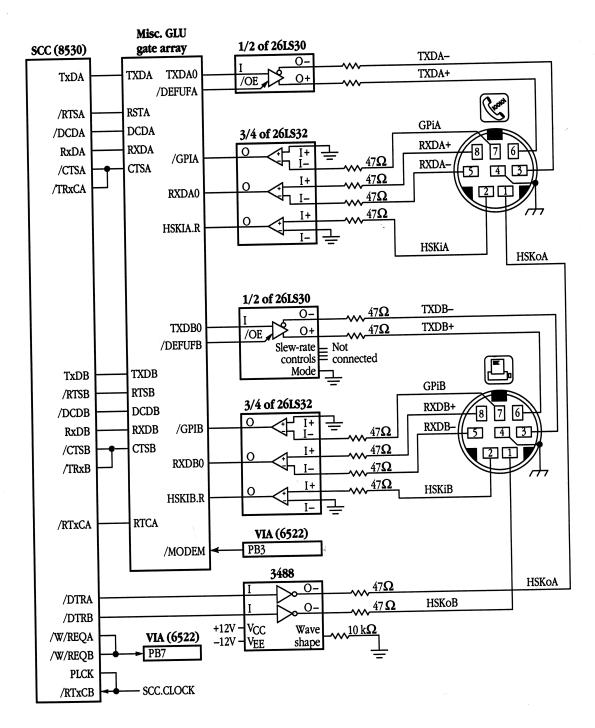

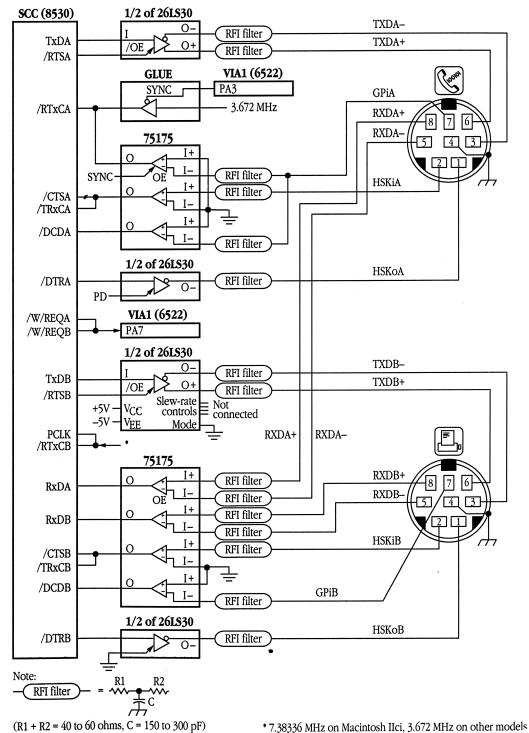

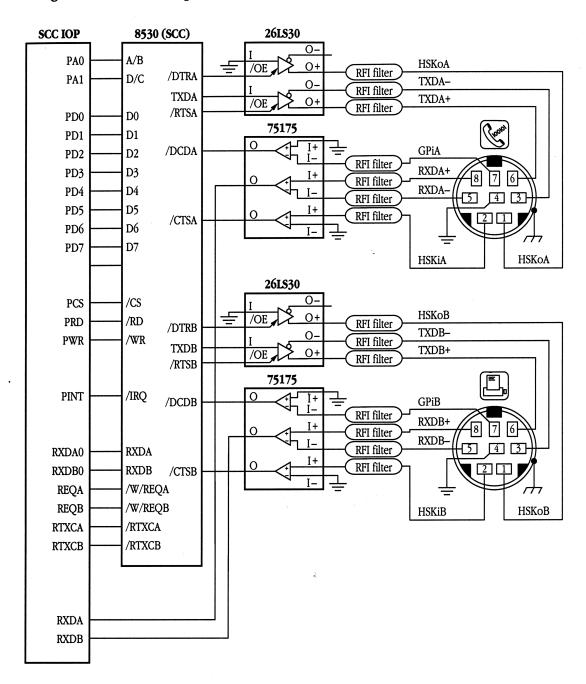

Serial I/O interface circuit diagrams / 365

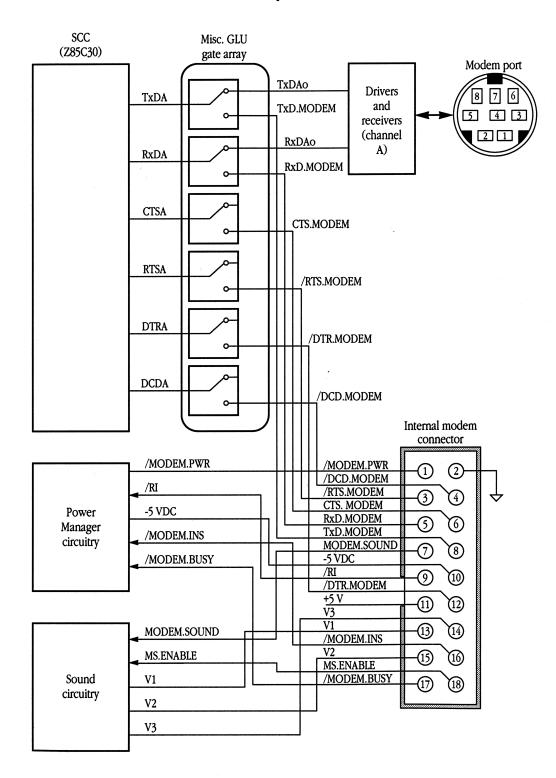

Modem slot in the Macintosh Portable / 371

Modem power control / 374

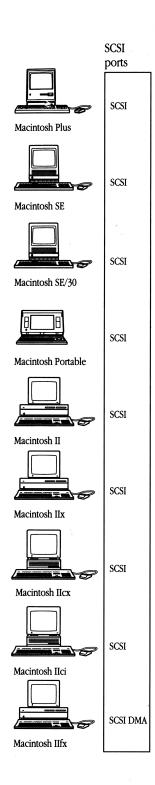

### 11 SCSI Ports / 375

Using the Small Computer System Interface (SCSI) / 377

SCSI connectors / 379

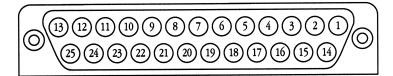

External SCSI connector / 379

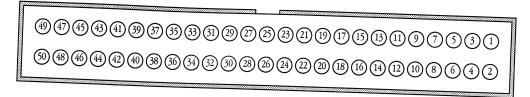

Internal SCSI connector / 380

Internal SCSI connector in the Macintosh Portable / 383

Circuit diagrams of the SCSI interface / 385

SCSI data transfers / 392

Handshaking for SCSI data transfers / 393

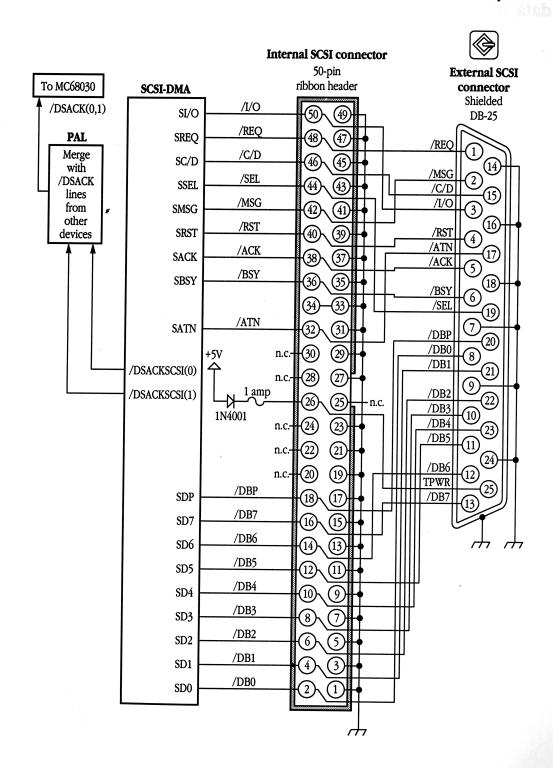

SCSI DMA in the Macintosh IIfx computer / 394

Operation of the SCSI DMA IC / 395

Slave mode / 395

Master mode / 395

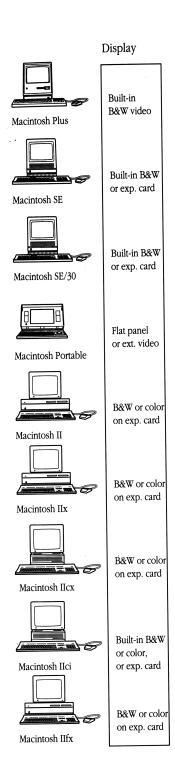

# 12 Displays / 397

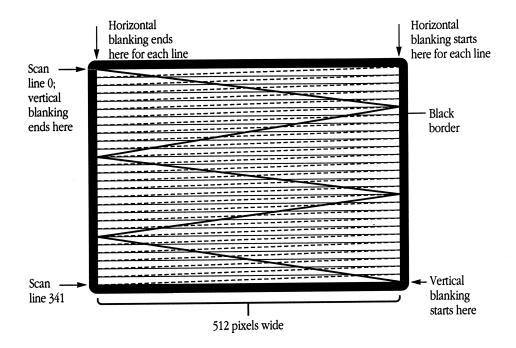

Built-in video display / 399

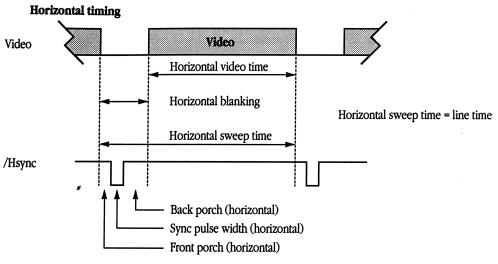

Video display scanning / 399

Video display circuits / 401

Video display buffers / 402

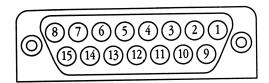

Expansion card video / 404

Video card features / 404

Video card components / 405

Timing generation / 405

Frame Buffer Controller (FBC) / 405

Video RAM / 406

CLUT DAC on the video card / 406

Declaration ROM / 407

External connector / 407

Detecting monitor type / 409

Video display in the Macintosh SE/30 computer / 409

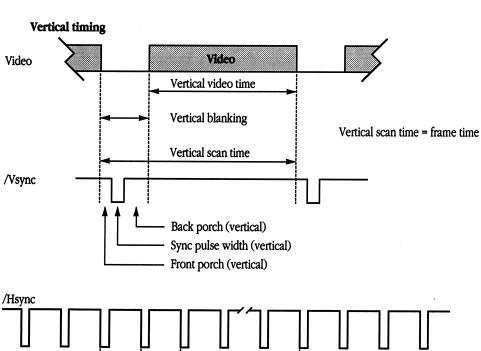

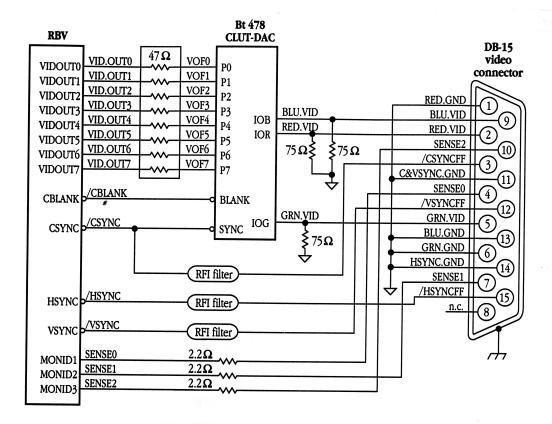

Video circuits in the Macintosh IIci computer / 410

Features of the built-in video circuits / 410

Detection of monitor type / 411

Pixels and colors / 411

Sizes of monitors and screen buffers / 411

Pseudo-slot video in the Macintosh IIci / 412

Built-in video components / 412

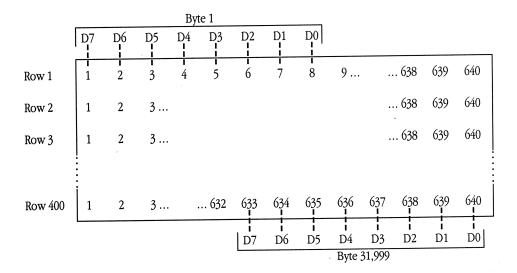

Screen buffer in the Macintosh IIci / 413

Video portion of the RBV / 414

CLUT DAC in the Macintosh IIci / 418

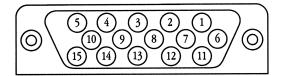

Video connector on the Macintosh IIci / 418

Displays on the Macintosh Portable / 421

Flat-panel display / 421

Contrast control / 422

Macintosh Portable external video / 423

### 13 Sound / 427

PWM sound system / 429

Sound buffers / 429

Generating sounds / 430

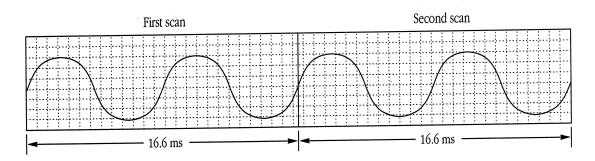

Scanning the sound buffers / 431

Circuit diagrams / 433

ASC sound system / 436

ASC sound modes / 436

Generating sounds / 437

Circuit diagrams / 439

## 14 Expansion Interfaces / 443

The 68000 processor-direct slot (PDS) / 445 68000 PDS on the Macintosh SE computer / 448 68000 PDS on the Macintosh Portable / 451 The 68030 processor-direct slot (PDS) / 454 The NuBus expansion interface / 461

# A Macintosh Family Hardware Specifications / 467

Macintosh Plus / 468

Environment / 469

Macintosh SE / 470

Environment / 471

Macintosh SE/30 / 472

Environment / 473

Macintosh Portable / 474

Environment / 475

Macintosh II / 476

Environment / 478

Macintosh IIx / 479

Environment / 480

Macintosh IIcx / 481

Environment / 482

Macintosh IIci / 483

Environment / 485

Macintosh IIfx / 486

Environment / 488

# B Hardware-Related Global Variables / 489

Glossary / 491

Index / 503

# Figures and tables

Preface About this book / xxix

1

| Table P-1    | Macintosh technical documentation / xxxv                    |  |  |

|--------------|-------------------------------------------------------------|--|--|

| Introduction | on to the Macintosh Hardware / 1                            |  |  |

| Figure 1-1   | Front view of the Macintosh 128K, 512K, and                 |  |  |

|              | 512K enhanced computers / 7                                 |  |  |

| Figure 1-2   | Back view of the Macintosh 128K, 512K, and                  |  |  |

|              | 512K enhanced computers / 7                                 |  |  |

| Figure 1-3   | Back view of the Macintosh Plus computer / 8                |  |  |

| Figure 1-4   | Front view of the Macintosh SE computer / 9                 |  |  |

| Figure 1-5   | Front view of the Macintosh SE/30 computer / 10             |  |  |

| Figure 1-6   | Back view of the Macintosh SE computer / 11                 |  |  |

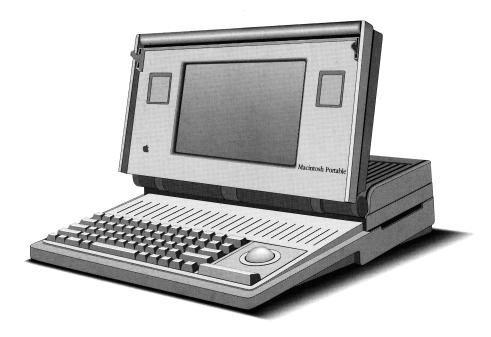

| Figure 1-7   | Front view of the Macintosh Portable computer / 12          |  |  |

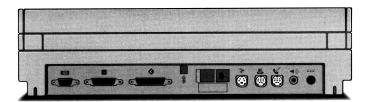

| Figure 1-8   | Back view of the Macintosh Portable computer / 13           |  |  |

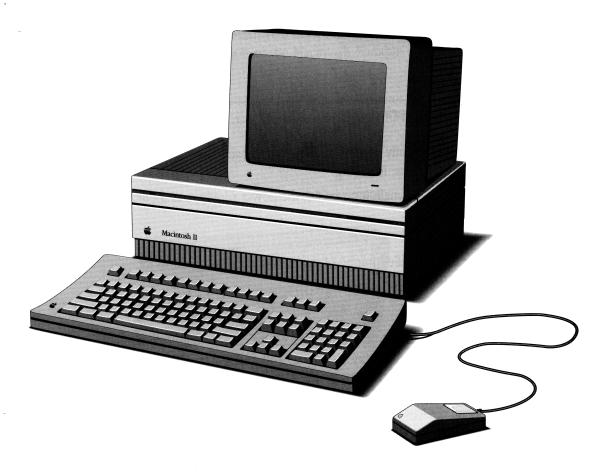

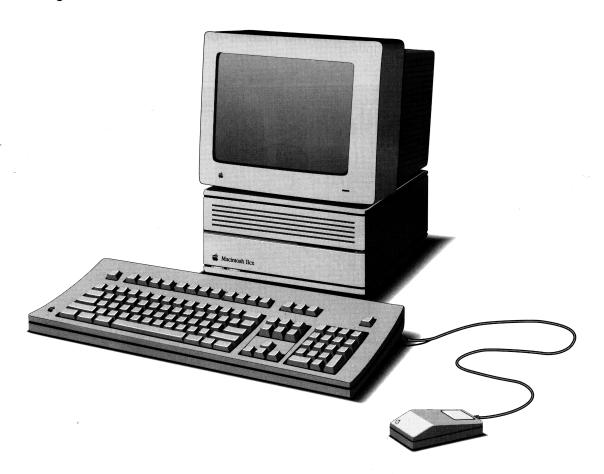

| Figure 1-9   | re 1-9 Front view of the Macintosh II, Macintosh IIx, and   |  |  |

|              | Macintosh IIfx computers / 14                               |  |  |

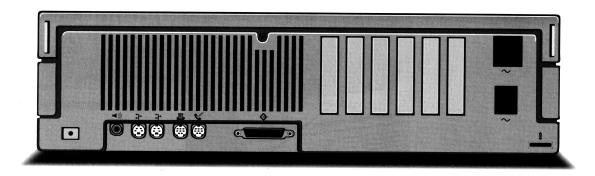

| Figure 1-10  | Back view of the Macintosh II, Macintosh IIx, and           |  |  |

|              | Macintosh IIfx computers / 15                               |  |  |

| Figure 1-11  | Front view of the Macintosh IIcx and                        |  |  |

|              | Macintosh IIci computers / 16                               |  |  |

| Figure 1-12  | Back view of the Macintosh IIcx computer / 17               |  |  |

| Figure 1-13  | Back view of the Macintosh IIci computer / 17               |  |  |

| Figure 1-14  |                                                             |  |  |

| Figure 1-15  | Interior view of the Macintosh SE computer / 20             |  |  |

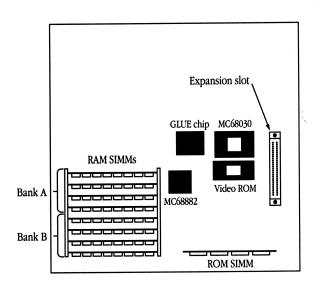

| Figure 1-16  | Interior view of the Macintosh SE/30 computer / 22          |  |  |

| Figure 1-17  |                                                             |  |  |

| Figure 1-18  | Interior view of the Macintosh II computer / 27             |  |  |

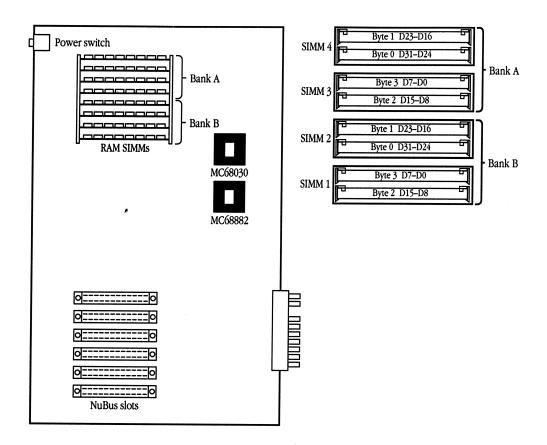

| Figure 1-19  | Interior view of the Macintosh IIcx computer / 30           |  |  |

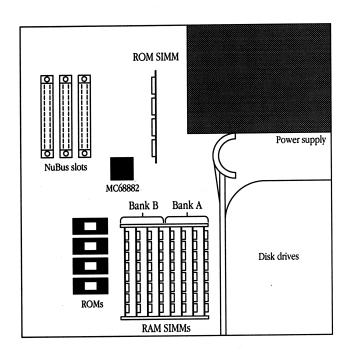

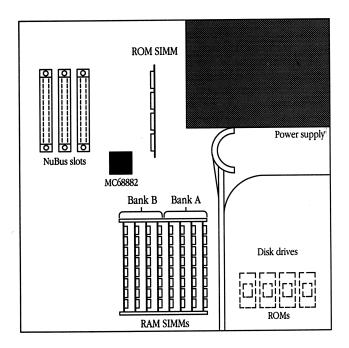

| Figure 1-20  |                                                             |  |  |

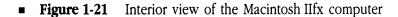

| Figure 1-21  | Interior view of the Macintosh IIfx computer / 32           |  |  |

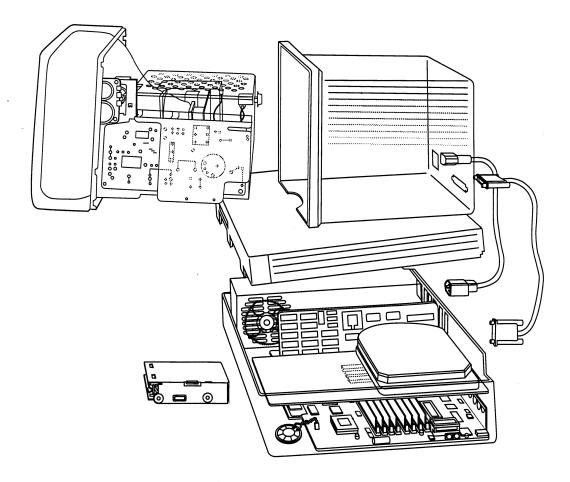

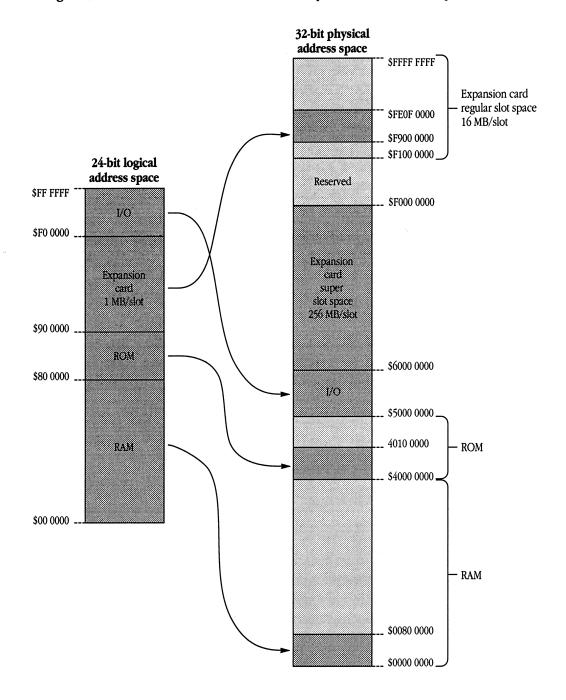

| Figure 1-22  | Simplified address map for the Macintosh 128K, 512K, and    |  |  |

|              | 512K enhanced computers / 36                                |  |  |

| Figure 1-23  | Simplified address map for the Macintosh Plus computer / 37 |  |  |

|              |                                                             |  |  |

| Figure 1-25 Simplified address map for t |                                              | Simplified address map for the Macintosh SE computer / 38 Simplified address map for the Macintosh Portable computer / 39 |  |  |

|------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

|                                          | Figure 1-26<br>Figure 1-27                   | Simplified address map for the Macintosh SE/30 computer / 4                                                               |  |  |

|                                          | Figure 1-28                                  | Simplified address map for the Macintosh IIci computer / 43                                                               |  |  |

|                                          | •                                            | Simplified address map for the Macintosh IIfx computer / 44                                                               |  |  |

|                                          | Figure 1-30                                  |                                                                                                                           |  |  |

|                                          | Table 1-1                                    | Summary of features of the Macintosh computers / 2                                                                        |  |  |

| 2                                        | Architecture of the Macintosh Computers / 47 |                                                                                                                           |  |  |

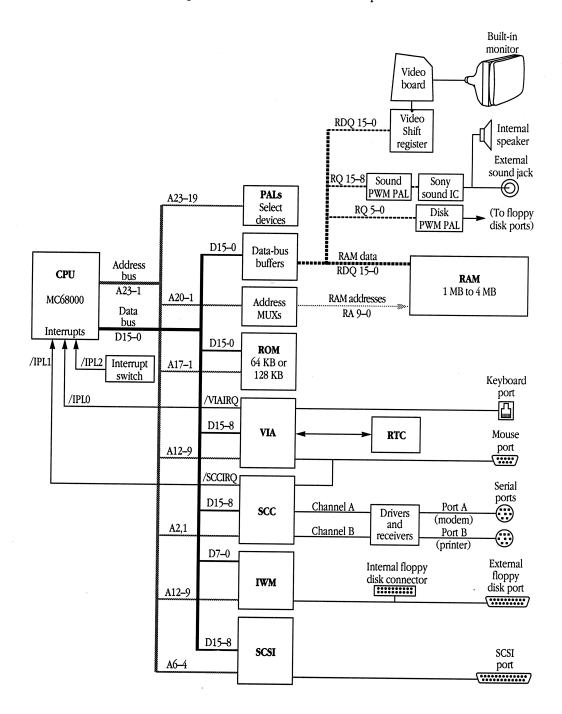

|                                          | Figure 2-1                                   | Block diagram of the Macintosh 128K, 512K, and                                                                            |  |  |

|                                          | 71 0.0                                       | 512K enhanced computers / 50                                                                                              |  |  |

|                                          | Figure 2-2                                   | Block diagram of the Macintosh Plus computer / 51                                                                         |  |  |

|                                          | Figure 2-3                                   | Block diagram of the Macintosh SE computer / 52                                                                           |  |  |

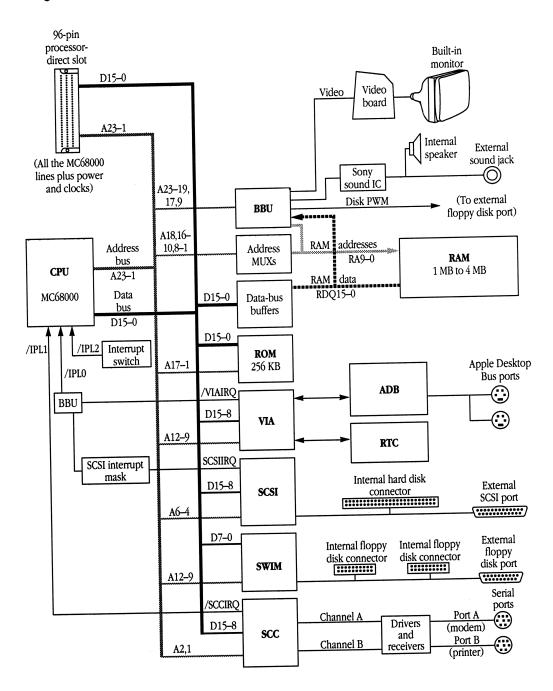

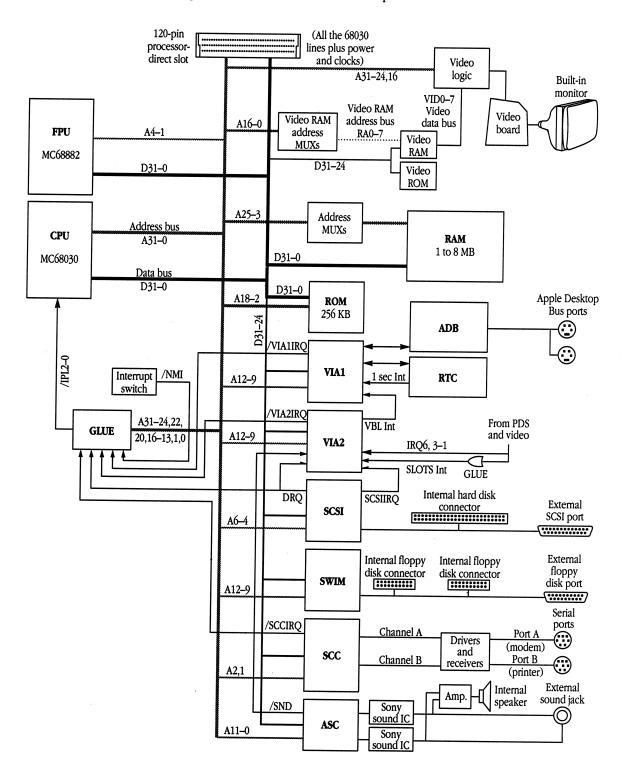

|                                          | Figure 2-4                                   | Block diagram of the Macintosh SE/30 computer / 53                                                                        |  |  |

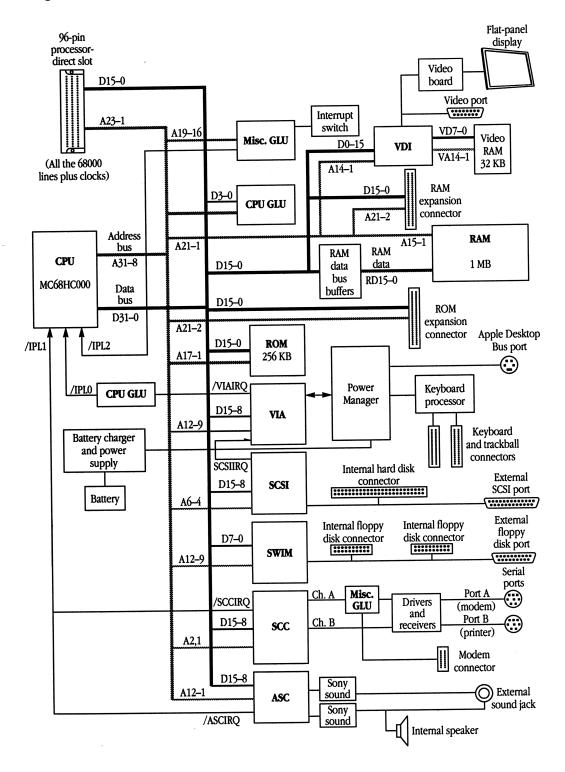

|                                          | Figure 2-5                                   | Block diagram of the Macintosh Portable computer / 54                                                                     |  |  |

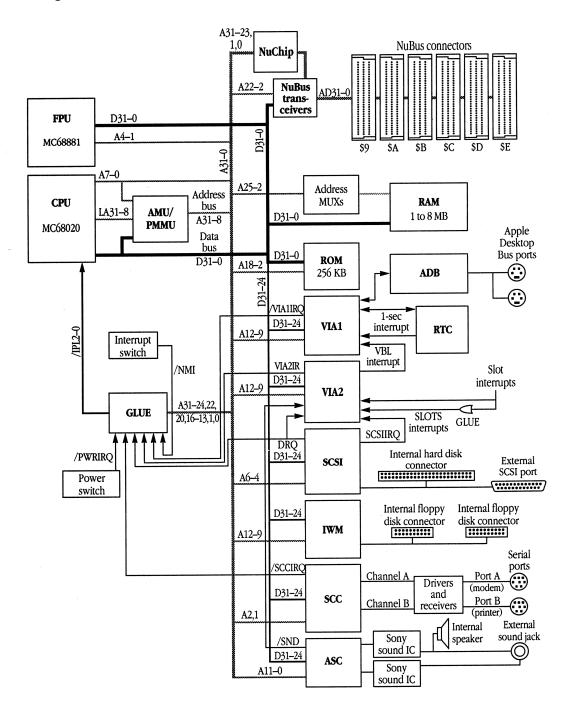

|                                          | Figure 2-6                                   | Block diagram of the Macintosh II computer / 56                                                                           |  |  |

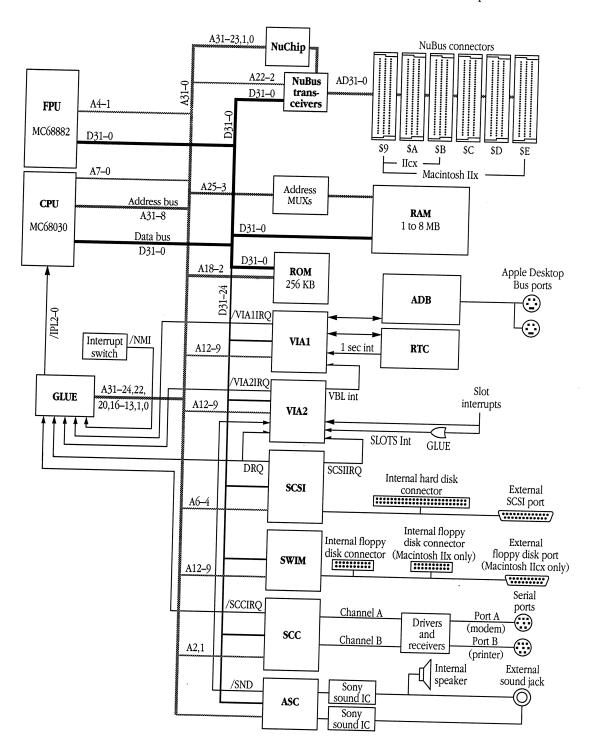

|                                          | Figure 2-7                                   | Block diagram of the Macintosh IIx and<br>Macintosh IIcx computers / 57                                                   |  |  |

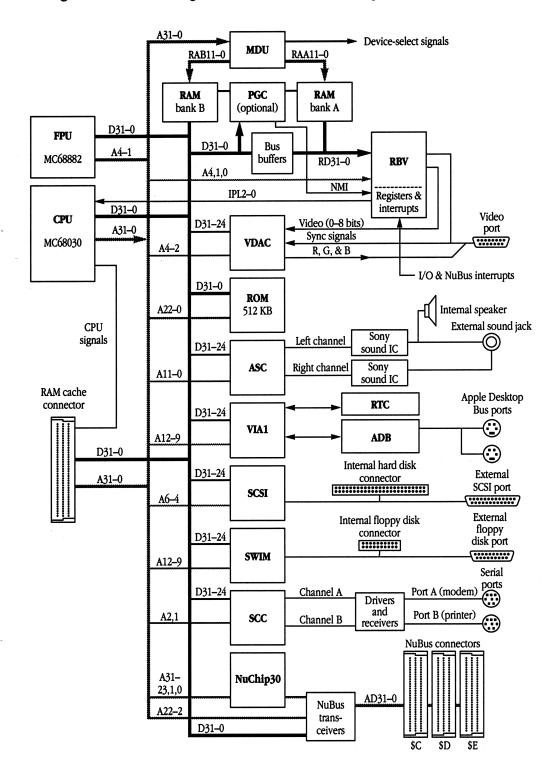

|                                          | Figure 2-8                                   | Block diagram of the Macintosh IIci computer / 58                                                                         |  |  |

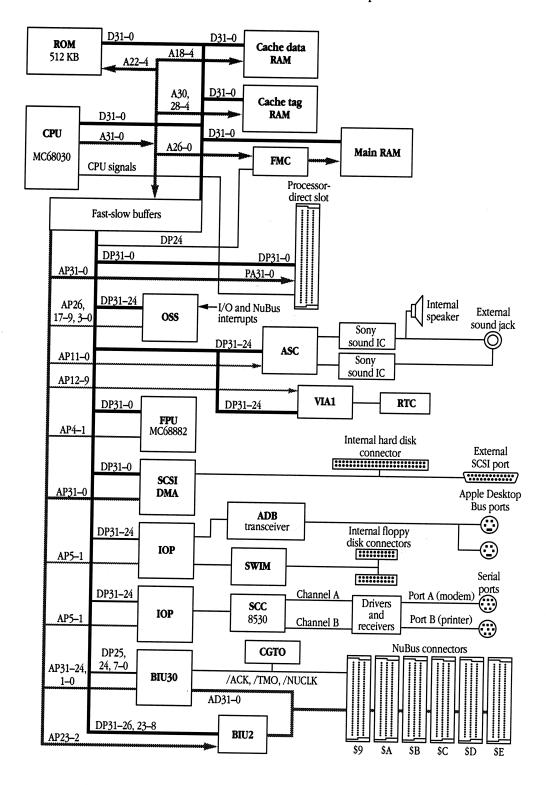

|                                          | Figure 2-9                                   | Block diagram of the Macintosh IIfx computer / 59                                                                         |  |  |

|                                          | Table 2-1                                    | Non-SCSI disk drives used by Macintosh computers / 81                                                                     |  |  |

| 3                                        | Processors                                   | and General Logic / 87                                                                                                    |  |  |

|                                          | Figure 3-1                                   | Address map for the Macintosh 512K computer / 123                                                                         |  |  |

|                                          | •                                            | Address map for the Macintosh Plus computer / 124                                                                         |  |  |

|                                          | Figure 3-3                                   | Address map for the Macintosh SE computer / 127                                                                           |  |  |

|                                          | Figure 3-4                                   | Address map for the Macintosh Portable computer / 129                                                                     |  |  |

|                                          | Figure 3-5                                   | Translation from 24-bit address map to 32-bit address map / 132                                                           |  |  |

|                                          | Figure 3-6                                   | Address map for the Macintosh SE/30 computer / 133                                                                        |  |  |

|                                          | •                                            | Address map for the Macintosh II, Macintosh IIx, and                                                                      |  |  |

|                                          | Figure 3-7                                   | Macintosh IIcx computers / 137                                                                                            |  |  |

/ 41

| Figure 3-8<br>Figure 3-9 | Address map for the Macintosh IIci computer / 142<br>Address map for the Macintosh IIfx computer / 143 |

|--------------------------|--------------------------------------------------------------------------------------------------------|

| Table 3-1                | Interrupt levels in the classic Macintosh computers / 92                                               |

| Table 3-2                | Interrupt levels in the Macintosh SE computer / 93                                                     |

| Table 3-3                | Interrupt levels in the Macintosh Portable computer / 95                                               |

| Table 3-4                | Interrupt levels in the Macintosh II computer / 99                                                     |

| Table 3-5                | Interrupt levels in Macintosh models with the MC68030 microprocessor / 101                             |

| Table 3-6                | Auxiliary processors used in Macintosh computers / 104                                                 |

| Table 3-7                | General logic circuits used in Macintosh computers / 111                                               |

| Table 3-8                | Macintosh 24-bit to 32-bit address translation / 131                                                   |

| Table 3-9                | Macintosh SE/30 expansion card address ranges / 134                                                    |

| Table 3-10               | Translations from NuBus addresses to main logic board                                                  |

|                          | addresses / 140                                                                                        |

| Table 3-11               | RTC bits in Macintosh VIA1 Data register B / 144                                                       |

| Versatile I              | nterface Adapter (VIA) ICs / 147                                                                       |

| Table 4-1                | Offsets of the VIA register locations / 159                                                            |

| Table 4-2                | Bits in VIA Data register A in the classic Macintosh                                                   |

|                          | computers / 160                                                                                        |

| Table 4-3                | Bits in VIA Data register A in the Macintosh SE                                                        |

|                          | computer / 161                                                                                         |

| Table 4-4                | Bits in VIA Data register A in the Macintosh Portable / 162                                            |

| Table 4-5                | Bits in VIA1 Data register A in the Macintosh SE/30,                                                   |

|                          | Macintosh II, Macintosh IIx, and Macintosh IIcx                                                        |

|                          | computers / 163                                                                                        |

| Table 4-6                | Bits in VIA1 Data register A in the Macintosh IIci                                                     |

|                          | computer / 164                                                                                         |

| Table 4-7                | Bits in VIA1 Data register A in the Macintosh IIfx                                                     |

| T 11 / 0                 | computer / 165                                                                                         |

| Table 4-8                | Identity codes in the Macintosh IIci and                                                               |

| T-1-1- / O               | Macintosh IIfx / 165                                                                                   |

| Table 4-9                | Bits in VIA2 Data register A / 166                                                                     |

| Table 4-10<br>Table 4-11 | VIA2 RAM size bits / 167                                                                               |

| 1 able 4-11              | Bits in VIA Data register B in the classic Macintosh                                                   |

| Table 4-12               | computers / 168                                                                                        |

| 1 adic 4-12              | Bits in VIA Data register B in the Macintosh SE computer / 168                                         |

| Table 4-13               | •                                                                                                      |

| 1 uDIC T-1)              | Bits in VIA Data register B in the Macintosh Portable                                                  |

|                          |                                                                                                        |

4

| Table 4-14                                                           | 0                                                                                                                          |  |  |  |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Table / 15                                                           | Macintosh II family / 171                                                                                                  |  |  |  |

| Table 4-15                                                           | 0                                                                                                                          |  |  |  |

| Table 4-16                                                           | 6 NuBus transfer acknowledge bits in VIA2 Data<br>Register B / 175                                                         |  |  |  |

| Table 4-17 Signals controlled by the VIA Peripheral Control register |                                                                                                                            |  |  |  |

|                                                                      | the classic Macintosh computers / 176                                                                                      |  |  |  |

| Table 4-18                                                           | Signals controlled by the Peripheral Control register in VIA in the Macintosh SE/30 and in VIA1 in the Macintosh II–family |  |  |  |

|                                                                      | computers / 177                                                                                                            |  |  |  |

| Table 4-19                                                           | Signals controlled by the VIA Peripheral Control register in                                                               |  |  |  |

|                                                                      | the Macintosh Portable computer / 178                                                                                      |  |  |  |

| Table 4-20                                                           | Signals controlled by the VIA2 Peripheral Control register / 178                                                           |  |  |  |

| Table 4-21                                                           | Bits in the Auxiliary Control register / 180                                                                               |  |  |  |

| Table 4-22                                                           | Bits 6 and 7 in the VIA Auxiliary Control register / 181                                                                   |  |  |  |

| Table 4-23                                                           | Offsets of Macintosh VIA timer latches / 182                                                                               |  |  |  |

| Table 4-24                                                           |                                                                                                                            |  |  |  |

| Macintosh computers / 185                                            |                                                                                                                            |  |  |  |

| Table 4-25                                                           | Bits in the Interrupt Flag register in the VIA in Macintosh SE                                                             |  |  |  |

|                                                                      | and in VIA1 in the Macintosh SE/30 and Macintosh II-family computers / 185                                                 |  |  |  |

| Table 4-26                                                           | Bits in the Interrupt Flag register in the VIA in the Macintosh                                                            |  |  |  |

| 14DIC 1-20                                                           | Portable computer / 186                                                                                                    |  |  |  |

| Table 4-27                                                           | Bits in the VIA2 Interrupt Flag register in the                                                                            |  |  |  |

|                                                                      | Macintosh SE/30 and Macintosh II-family computers / 186                                                                    |  |  |  |

| Memory /                                                             | 189                                                                                                                        |  |  |  |

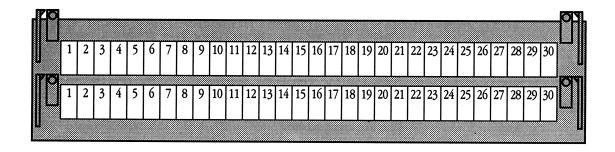

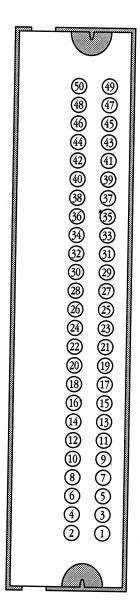

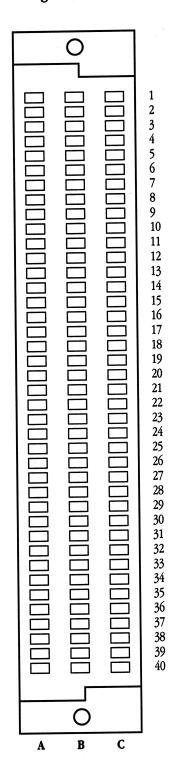

| Figure 5-1                                                           | Pinout of the RAM SIMM socket in the Macintosh Plus and                                                                    |  |  |  |

| T: 50                                                                | Macintosh SE computers / 199                                                                                               |  |  |  |

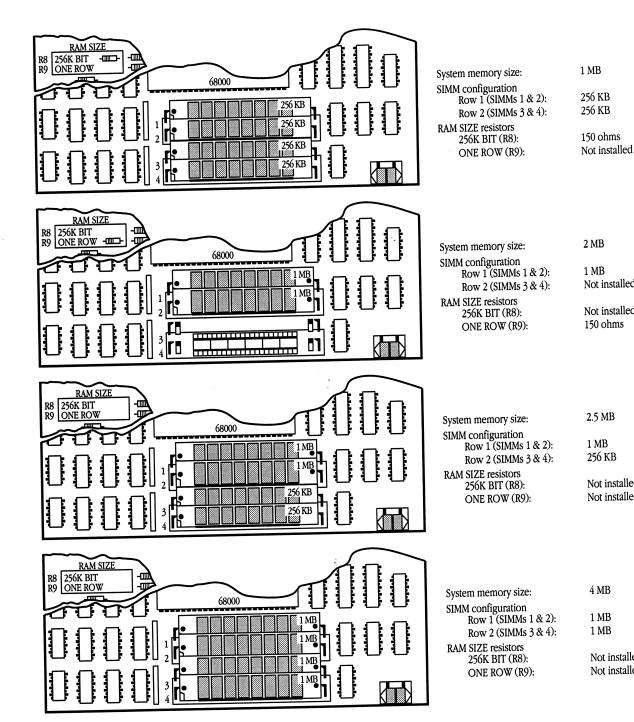

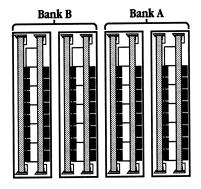

| Figure 5-2                                                           | SIMM configurations in the Macintosh Plus computer / 202                                                                   |  |  |  |

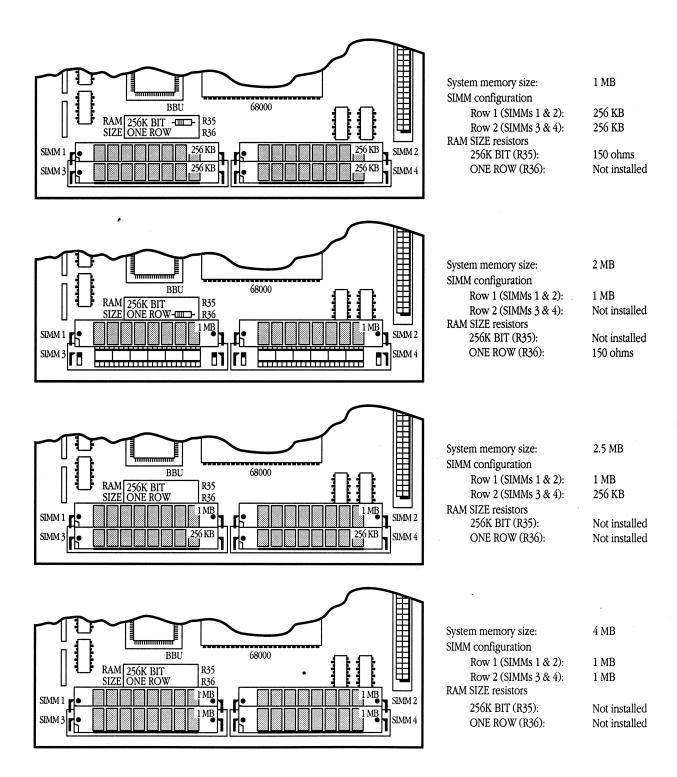

| Figure 5-3                                                           |                                                                                                                            |  |  |  |

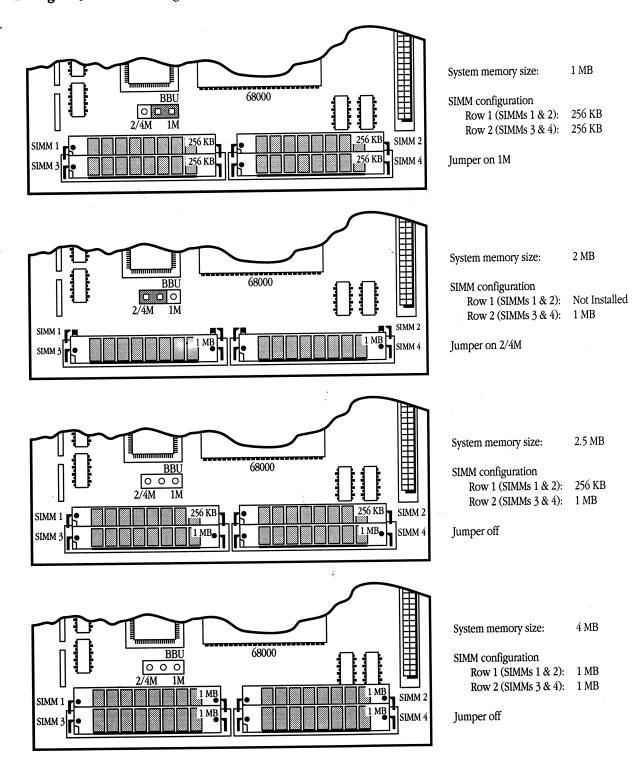

| Figure 5-4                                                           | 1                                                                                                                          |  |  |  |

| Figure 5-5                                                           | Pinout of the RAM expansion connector in the Macintosh                                                                     |  |  |  |

|                                                                      | Portable computer / 207                                                                                                    |  |  |  |

| Figure 5-6                                                           | RAM SIMM locations in the Macintosh SE/30 computer / 216                                                                   |  |  |  |

| Figure 5-7                                                           | RAM SIMM locations in the Macintosh II and Macintosh IIx                                                                   |  |  |  |

| -                                                                    | computers / 217                                                                                                            |  |  |  |

| Figure 5-8                                                           | RAM SIMM locations in the Macintosh IIcx computer / 218                                                                    |  |  |  |

| Figure 5-9                                                           | RAM SIMM locations in the Macintosh IIci computer / 218                                                                    |  |  |  |

5

| Figure 5-10<br>Figure 5-11<br>Figure 5-12 | Macintosh II-family computers / 220                                                                                                                        |  |  |  |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

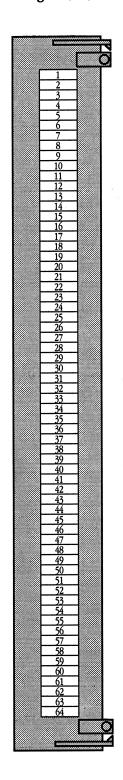

| Figure 5-13                               | Pinout of the ROM SIMM socket / 236                                                                                                                        |  |  |  |

| Table 5-1                                 | RAM addresses in Macintosh computers with an MC68000 processor / 191                                                                                       |  |  |  |

| Table 5-2                                 | RAM addresses in the Macintosh SE/30 and Macintosh II–family computers / 193                                                                               |  |  |  |

| Table 5-3<br>Table 5-4                    | RAM access rates in the Macintosh family computers / 194 Signal assignments for the RAM SIMM socket in the Macintosh Plus and Macintosh SE computers / 200 |  |  |  |

| Table 5-5                                 | Signal assignments for the RAM expansion connector in the Macintosh Portable computer / 208                                                                |  |  |  |

| Table 5-6                                 | Signal assignments for RAM SIMM sockets in the Macintosh SE/30 and Macintosh II–family computers (except the Macintosh IIfx) / 212                         |  |  |  |

| Table 5-7                                 |                                                                                                                                                            |  |  |  |

| Table 5-8                                 | Signal assignments for the cache card connector / 227                                                                                                      |  |  |  |

| Table 5-9                                 | ROM access rates / 231                                                                                                                                     |  |  |  |

| Table 5-10                                | Signal assignments for the ROM expansion connector in the Macintosh Portable computer / 234                                                                |  |  |  |

| Table 5-11                                | <u> -</u>                                                                                                                                                  |  |  |  |

| Power Sup                                 | plies / 239                                                                                                                                                |  |  |  |

| Figure 6-1                                | Pinout of the power supply connector on the Macintosh Plus computer / 246                                                                                  |  |  |  |

| Figure 6-2                                | Pinout of the power supply connector on the Macintosh SE and Macintosh SE/30 computers / 247                                                               |  |  |  |

| Figure 6-3                                | Pinout of the power and video connector from the analog<br>board to the logic board in the Macintosh SE and<br>Macintosh SE/30 computers / 248             |  |  |  |

| Figure 6-4                                | Pinout of the power connector on the Macintosh Portable computer / 249                                                                                     |  |  |  |

| Figure 6-5                                | Pinout of the power supply connector on the Macintosh IIcx and Macintosh IIci computers / 250                                                              |  |  |  |

| Figure 6-6                                | Pinout of the power supply connector in the Macintosh II,<br>Macintosh IIx, and Macintosh IIfx computers / 251                                             |  |  |  |

| Figure 6-7                                | Power-control circuit in the Macintosh II–family computers / 272                                                                                           |  |  |  |

| Table 6-1  | Signal assignments for the power supply connector on the Macintosh Plus computer / 246                                                                |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 6-2  | Signal assignments for the power supply connector on the Macintosh SE and Macintosh SE/30 computers / 247                                             |

| Table 6-3  | Signal assignments for the power and video connector from the analog board to the logic board in the Macintosh SE and Macintosh SE/30 computers / 248 |

| Table 6-4  | Signal assignments for the power connector on the Macintosh Portable computer / 249                                                                   |

| Table 6-5  | Signal assignments for the power supply connector on the Macintosh IIcx and Macintosh IIci computers / 250                                            |

| Table 6-6  | Signal assignments for the power supply connector in the Macintosh II, Macintosh IIx, and Macintosh IIfx computers / 251                              |

| Table 6-7  | AC input requirements for the Macintosh Plus computer / 253                                                                                           |

| Table 6-8  | AC input requirements for the Macintosh SE and Macintosh SE/30 computers / 254                                                                        |

| Table 6-9  | AC input requirements for the battery charger in the Macintosh Portable computer / 255                                                                |

| Table 6-10 | AC input requirements for the Macintosh IIcx and Macintosh IIci / 256                                                                                 |

| Table 6-11 | AC input requirements for the Macintosh II, Macintosh IIx, and Macintosh IIfx computers / 257                                                         |

| Table 6-12 | Power supply output limits in the Macintosh Plus computer / 258                                                                                       |

| Table 6-13 | Total power at DC output loads for the Macintosh Plus computer / 258                                                                                  |

| Table 6-14 | DC output ripple and switching noise for the Macintosh Plus computer / 258                                                                            |

| Table 6-15 | Power supply output limits for the Macintosh SE and Macintosh SE/30 computers / 259                                                                   |

| Table 6-16 | Total power at DC output loads for the Macintosh SE and Macintosh SE/30 computers / 259                                                               |

| Table 6-17 | DC output ripple and switching noise for the Macintosh SE and Macintosh SE/30 computers / 260                                                         |

| Table 6-18 | Output limits for the voltage-control circuits in the Macintosh Portable computer / 261                                                               |

| Table 6-19 | Total power at DC output loads for the Macintosh Portable computer / 261                                                                              |

Table 6-20 Power supply output limits in the Macintosh IIcx and Macintosh IIci computers / 261

| Table 6-21 | Total power at DC output loads for the Macintosh IIcx and                                      |

|------------|------------------------------------------------------------------------------------------------|

|            | Macintosh IIci computers / 262                                                                 |

| Table 6-22 | DC output ripple and switching noise for the Macintosh IIcx and Macintosh IIci computers / 262 |

| Table 6-23 |                                                                                                |

|            | Macintosh IIx, and Macintosh IIfx computers / 263                                              |

| Table 6-24 |                                                                                                |

|            | Macintosh IIx, and Macintosh IIfx computers / 263                                              |

| Table 6-25 |                                                                                                |

|            | Macintosh IIx, and Macintosh IIfx computers / 264                                              |

| Table 6-26 |                                                                                                |

| 14010 0 20 | the Macintosh II–family computers / 265                                                        |

|            | the Macinton is family computers / 20)                                                         |

| Macintosl  | n Plus Mouse and Keyboard / 273                                                                |

| Figure 7-1 | Mouse mechanism in the Macintosh Plus computer / 275                                           |

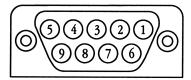

| Figure 7-2 | Pinout of the DB-9 mouse connector in the Macintosh Plus                                       |

|            | computer / 278                                                                                 |

| Figure 7-3 | Circuit diagram of the mouse port in the Macintosh Plus                                        |

|            | computer / 279                                                                                 |

| Figure 7-4 | Pinout of the RJ-11 keyboard connector in the Macintosh                                        |

|            | Plus computer / 280                                                                            |

| Figure 7-5 | Circuit diagram of the keyboard interface in the Macintosh                                     |

|            | Plus computer / 281                                                                            |

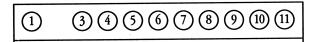

| Figure 7-6 | Key-down transition codes in the Macintosh Plus computer                                       |

|            | (hexadecimal) / 284                                                                            |

| Figure 7-7 | Keyboard transition codes in the Macintosh 128K,                                               |

|            | Macintosh 512K, and Macintosh 512K enhanced computers                                          |

|            | (hexadecimal) / 285                                                                            |

| Figure 7-8 | Key-down transition codes for the separate keypad                                              |

|            | (hexadecimal) / 286                                                                            |

| m 11 = 4   |                                                                                                |

| Table 7-1  | Mouse-motion signals in the Macintosh Plus computer / 276                                      |

| Table 7-2  | Signal assignments for the DB-9 mouse connector in the                                         |

| m 11 = 0   | Macintosh Plus computer / 278                                                                  |

| Table 7-3  | Signal assignments for the keyboard connector in the                                           |

| m 11 - /   | Macintosh Plus computer / 281                                                                  |

| Table 7-4  | Keyboard commands in the Macintosh Plus computer / 283                                         |

|            |                                                                                                |

7

## 8 Apple Desktop Bus / 287

|             | -                                                           |

|-------------|-------------------------------------------------------------|

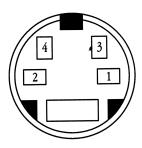

| Figure 8-1  | Pinout of the ADB connector / 291                           |

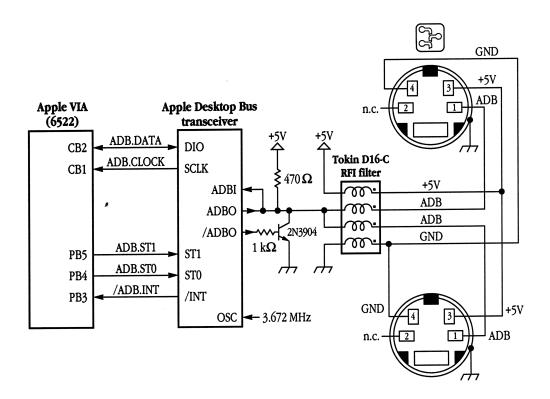

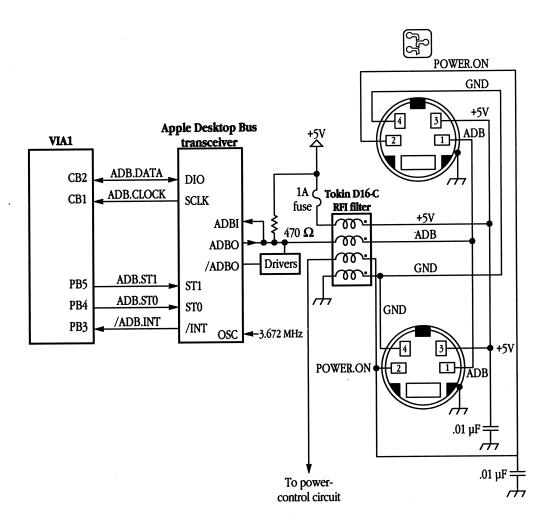

| Figure 8-2  | Circuit diagram for the ADB interface on Macintosh SE and   |

|             | Macintosh SE/30 computers / 293                             |

| Figure 8-3  | Circuit diagram for the ADB interface on Macintosh II,      |

|             | Macintosh IIx, Macintosh IIcx, and Macintosh IIci           |

|             | computers / 294                                             |

| Figure 8-4  | Circuit diagram for the ADB interface on the Macintosh IIfx |

|             | computer / 295                                              |

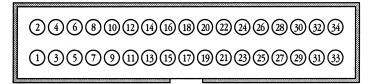

| Figure 8-5  | Pinout of the keyboard and trackball connectors on the      |

|             | Macintosh Portable computer / 297                           |

| Figure 8-6  | Circuit diagram of the ADB interface on the Macintosh       |

|             | Portable computer / 299                                     |

| Figure 8-7  | Mechanism of the Apple Standard Mouse / 302                 |

| Figure 8-8  | Trackball direction conventions / 305                       |

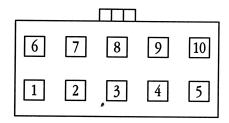

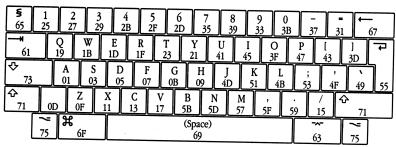

| Figure 8-9  | Key-down transition codes generated by the Apple Standard   |

|             | Keyboard / 306                                              |

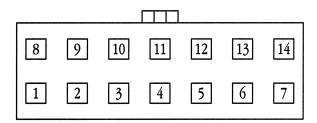

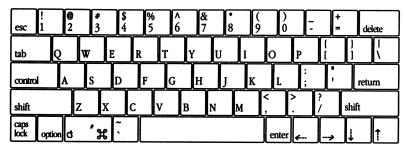

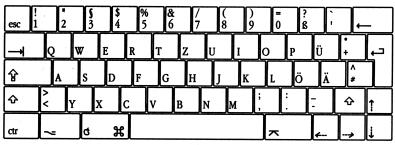

| Figure 8-10 | Key-down transition codes generated by the Apple            |

|             | Extended Keyboard / 308                                     |

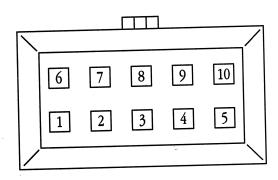

| Figure 8-11 | Keyboard layout on the Macintosh Portable computer / 311    |

| Figure 8-12 | Keypad layout on the Macintosh Portable computer / 311      |

| Figure 8-13 |                                                             |

| Figure 8-14 |                                                             |

| Figure 8-15 | ADB Service Request signal / 318                            |

| Table 8-1   | Signal assignments for the ADB connector / 291              |

| Table 8-2   | Electrical characteristics of the ADB transceiver / 292     |

| Table 8-3   | Signal assignments for the keyboard and trackball           |

|             | connectors on the Macintosh Portable computer / 298         |

| Table 8-4   | ADB transceiver register 0 in the Apple Standard            |

|             | Mouse / 301                                                 |

| Table 8-5   | Signal assignments for the connector on the trackball / 303 |

| Table 8-6   | Key code reassignments for the Apple Standard               |

|             | Keyboard / 306                                              |

| Table 8-7   | Register 0 in the Apple Standard Keyboard / 307             |

| Table 8-8   | Register 2 in the Apple Standard Keyboard / 307             |

| Table 8-9   | Key code reassignments in the Apple Extended                |

|             | Keyboard / 309                                              |

| Table 8-10  | Register 0 in the Apple Extended Keyboard / 309             |

| Table 8-11  | •                                                           |

| Table 8-12  | ADB transaction states / 314                                |

| Table 8-13  | Command byte syntax / 315                                   |

| Table 8-14                                                     | ADB timing specifications / 319                                                                                                |  |  |  |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Table 8-15                                                     | Bits in device register 3 / 322                                                                                                |  |  |  |

| Table 8-16                                                     | Device addresses / 322                                                                                                         |  |  |  |

| Table 8-17                                                     | Device Handler IDs reserved for special functions / 324                                                                        |  |  |  |

|                                                                |                                                                                                                                |  |  |  |

| Floppy Di                                                      | sk Interfaces / 327                                                                                                            |  |  |  |

| Figure 9-1                                                     | NRZI encoding (used with GCR formatting) / 331                                                                                 |  |  |  |

| Figure 9-2                                                     | MFM encoding / 332                                                                                                             |  |  |  |

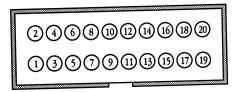

| Figure 9-3                                                     | Pinout of the connector for the internal 800 KB floppy disk drive / 334                                                        |  |  |  |

| Figure 9-4                                                     | Pinout of the connector for the external floppy disk drive on the Macintosh Plus and Macintosh SE computers / 337              |  |  |  |

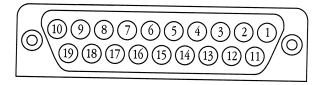

| Figure 9-5                                                     | Circuit diagram of the floppy disk drive interface on the Macintosh Plus computer / 339                                        |  |  |  |

| Figure 9-6                                                     | Circuit diagram of the floppy disk drive interface on the original Macintosh SE computer / 340                                 |  |  |  |

| Figure 9-7                                                     | Circuit diagram of the floppy disk drive interface on the Macintosh II computer / 341                                          |  |  |  |

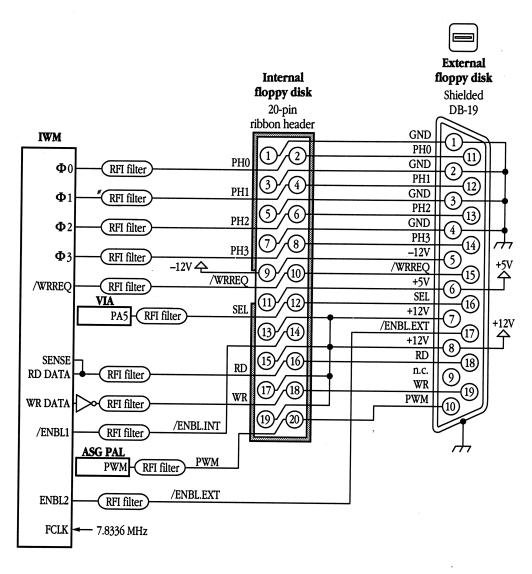

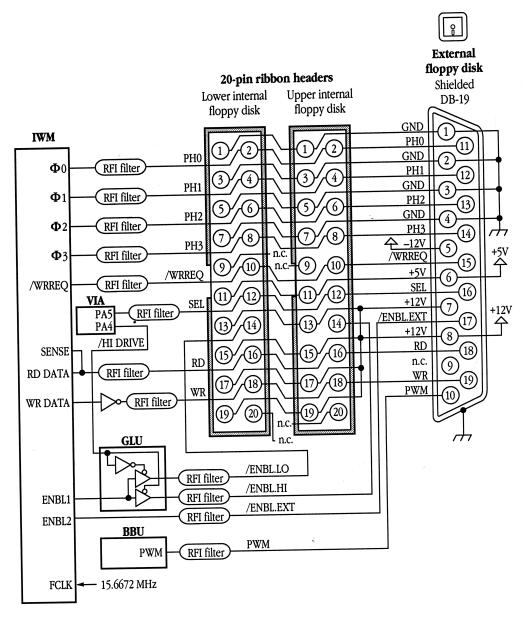

| Figure 9-8                                                     | Pinout of the connector for the internal FDHD drive / 345                                                                      |  |  |  |

| Figure 9-9                                                     | Pinout for the connector for the external FDHD drive / 348                                                                     |  |  |  |

| Figure 9-10 Circuit diagram of the FDHD drive interface on the |                                                                                                                                |  |  |  |

|                                                                | Macintosh SE FDHD and Macintosh SE/30 computers / 351                                                                          |  |  |  |

| Figure 9-11                                                    | Circuit diagram of the FDHD drive interface on the                                                                             |  |  |  |

|                                                                | Macintosh Portable computer / 352                                                                                              |  |  |  |

| Figure 9-12                                                    | Circuit diagram of the FDHD drive interface on the                                                                             |  |  |  |

|                                                                | Macintosh IIx computer / 353                                                                                                   |  |  |  |

| Figure 9-13                                                    | Circuit diagram of the FDHD drive interface on the Macintosh IIcx and Macintosh IIci computers / 354                           |  |  |  |

| Figure 9-14                                                    | Circuit diagram of the FDHD drive interface on the                                                                             |  |  |  |

|                                                                | Macintosh IIfx computer / 355                                                                                                  |  |  |  |

| Table 9-1                                                      | Basic features of Macintosh floppy disk drives / 330                                                                           |  |  |  |

| Table 9-2                                                      | Macintosh models that use the 800 KB floppy disk drive / 333                                                                   |  |  |  |

| Table 9-3                                                      | Signal assignments for the internal floppy disk drive connector on the Macintosh Plus computer / 335                           |  |  |  |

| Table 9-4                                                      | Signal assignments for the connector for the internal floppy                                                                   |  |  |  |

|                                                                | disk drive on the Macintosh SE and Macintosh II                                                                                |  |  |  |

|                                                                | computers / 336                                                                                                                |  |  |  |

| Table 9-5                                                      | Signal assignments for the connector for the external floppy disk drive on the Macintosh Plus and Macintosh SE computers / 338 |  |  |  |

|                                                                | <del>-</del>                                                                                                                   |  |  |  |

9

Macintosh models that use the Apple FDHD drive / 344 Table 9-6 Signal assignments for the internal FDHD drive connectors Table 9-7

on the Macintosh IIx, Macintosh IIcx, Macintosh IIci, and

Macintosh IIfx computers / 346

- Signal assignments for the internal FDHD drive connector on Table 9-8 the Macintosh SE FDHD, Macintosh SE/30, and Macintosh Portable computers / 347

- Signal assignments for the external FDHD drive connector on Table 9-9 the Macintosh IIcx and Macintosh IIci computers / 349

- Signal assignments for the external FDHD drive connector on Table 9-10 the Macintosh SE FDHD, Macintosh SE/30, and Macintosh Portable computers / 350

### 10 Serial I/O Ports / 357

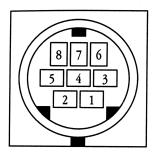

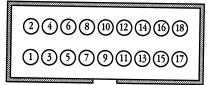

- Figure 10-1 Pinout of the mini 8-pin serial port connectors / 360

- Figure 10-2 Circuit diagram of the serial I/O interface in the Macintosh Plus computer / 366

- Figure 10-3 Circuit diagram of the serial I/O interface in the Macintosh SE computer / 367

- Figure 10-4 Circuit diagram of the serial I/O interface in the Macintosh Portable computer / 368

- Figure 10-5 Circuit diagram of the serial I/O interface in the Macintosh SE/30, Macintosh II, Macintosh IIx, Macintosh IIcx, and Macintosh IIci computers / 369

- Figure 10-6 Circuit diagram of the serial I/O interface in the Macintosh IIfx computer / 370

- Figure 10-7 Pinout of the modem connector on the Macintosh Portable computer / 371

- Figure 10-8 Circuit diagram of the modem interface on the Macintosh Portable computer / 372

- Table 10-1 Signal assignments for the mini 8-pin serial port connectors / 360

- Table 10-2 Addresses of SCC registers / 364

- Signal assignments for the modem connector in the Table 10-3 Macintosh Portable computer / 373

### 11 SCSI Ports / 375

- Figure 11-1 Pinout of the external SCSI connector on the Macintosh computers / 379

- Figure 11-2 Pinout of the internal SCSI connector on the Macintosh computers / 381

- Figure 11-3 Pinout of the internal SCSI connector in the Macintosh Portable computer / 383

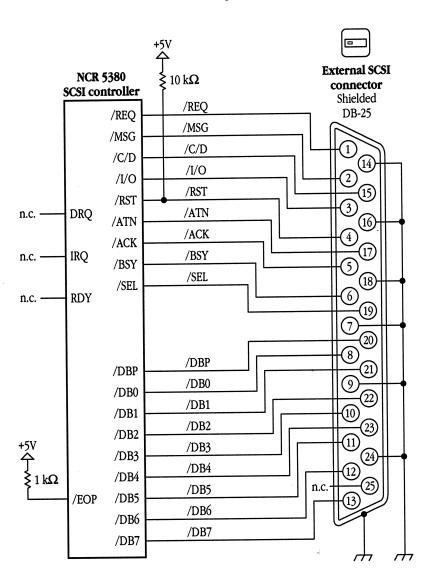

- Figure 11-4 Circuit diagram of the SCSI interface on the Macintosh Plus computer / 386

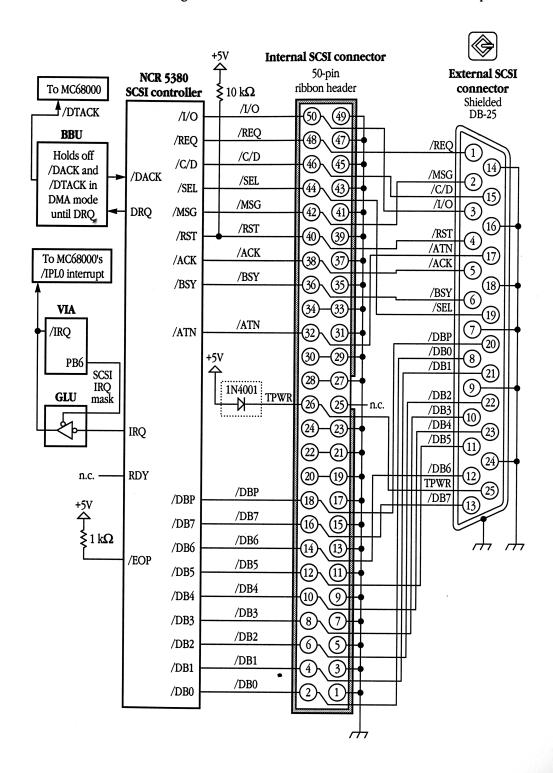

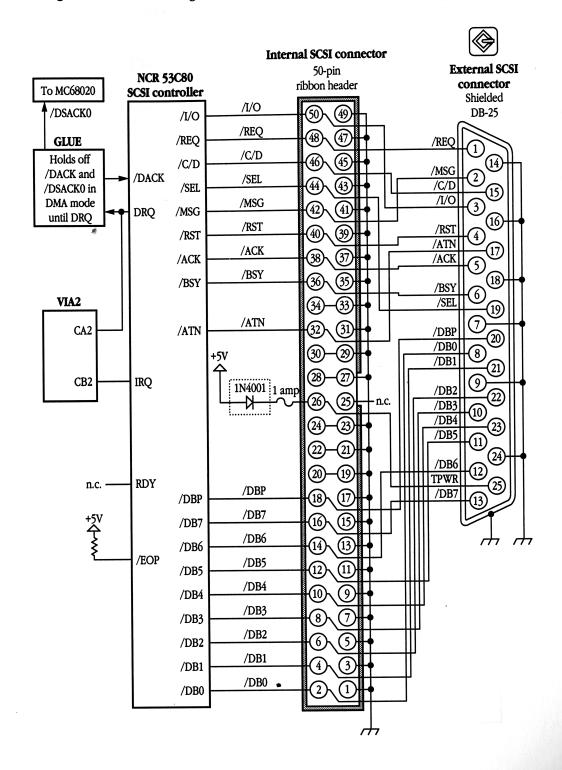

- Figure 11-5 Circuit diagram of the SCSI interface on the Macintosh SE computer / 387

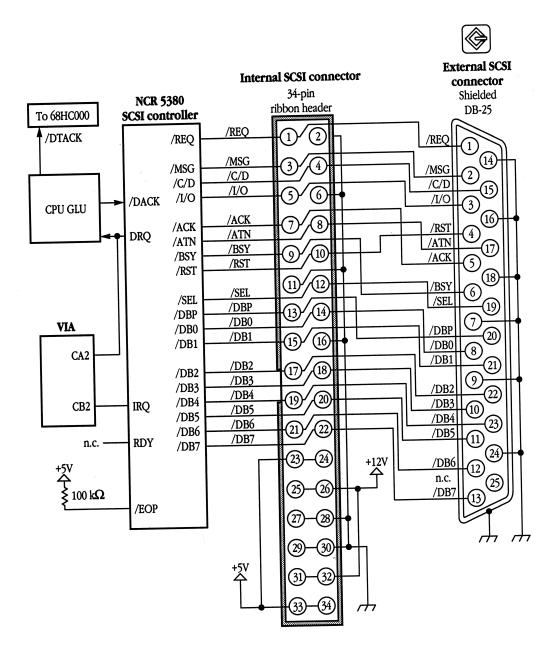

- Figure 11-6 Circuit diagram of the SCSI interface on the Macintosh Portable computer / 388

- Figure 11-7 Circuit diagram of the SCSI interface on the Macintosh II computer / 389

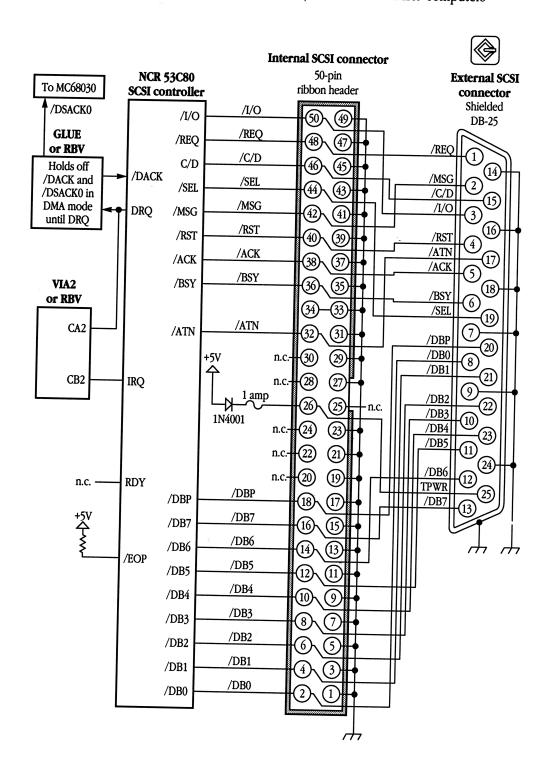

- Figure 11-8 Circuit diagram of the SCSI interface on the Macintosh SE/30, Macintosh IIx, Macintosh IIcx, and Macintosh IIci computers / 390

- Figure 11-9 Circuit diagram of the SCSI interface on the Macintosh IIfx computer / 391

- Table 11-1 Signal assignments for the external SCSI connector on the Macintosh computers / 380

- Table 11-2 Signal assignments for the internal SCSI connector on the Macintosh computers / 381

- Table 11-3 Signal assignments for the internal SCSI connector in the Macintosh Portable computer / 384

## 12 Displays / 397

- Figure 12-1 Video scanning pattern in the Macintosh computers with built-in video displays / 400

- Figure 12-2 Pinout of the external connector on the Macintosh II Video Card / 408

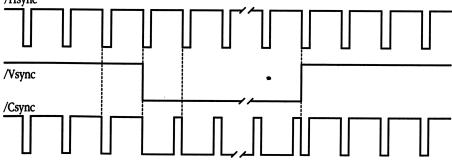

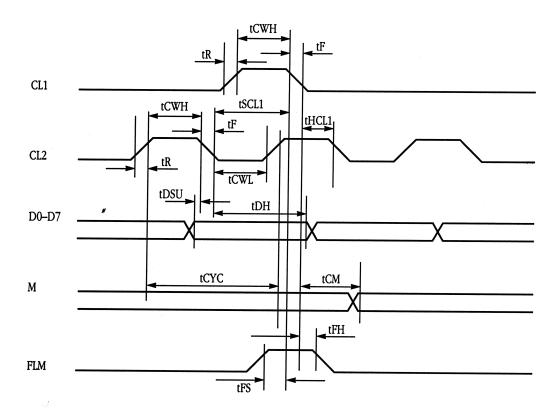

- Figure 12-3 Video timing parameters / 417

- Figure 12-4 Video interface circuit in the Macintosh IIci / 419

- Figure 12-5 Display pixel map / 422

- Figure 12-6 Pinout of the external video connector on the Macintosh Portable computer / 423

- Figure 12-7 Timing diagram for external video in the Macintosh Portable computer / 425

- Table 12-1 Signal assignments for the external connector of the Macintosh II Video Card / 408

- Table 12-2 Sense line values for different types of monitors / 409

- Table 12-3 Screen sizes and buffer sizes supported by the Macintosh IIci computer / 411

- Table 12-4 Time spent making video RAM accesses in bank A / 414

- Table 12-5 Horizontal video timing in the Macintosh IIci computer / 416

- Table 12-6 Vertical video timing in the Macintosh IIci computer / 416

- Table 12-7 Signals on the video connector in the Macintosh IIci / 420

- Table 12-8 Sense line values for video monitors on the Macintosh IIci computer / 420

- Signal assignments for the external video connector on the Table 12-9 Macintosh Portable computer / 424

- Table 12-10 External video timing limits / 425

#### Sound / 427 13

- Figure 13-1 A sound waveform with a frequency of 2 times the scan rate / 432

- Figure 13-2 A sound waveform with a frequency that is not a multiple of the scan rate / 432

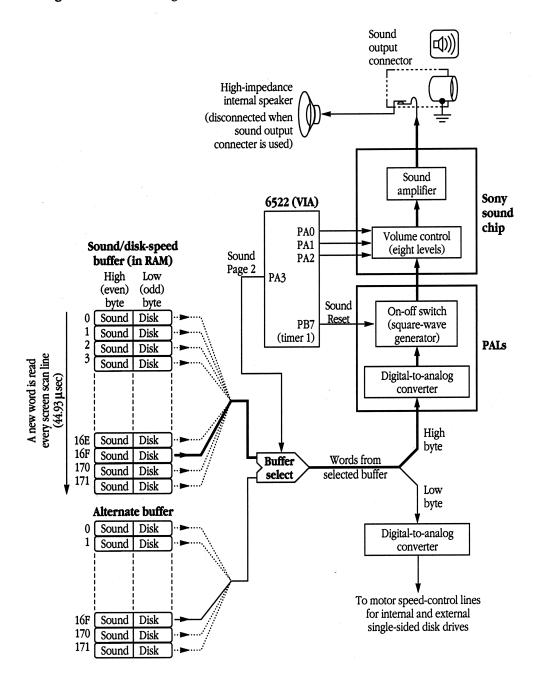

- Figure 13-3 Block diagram of the PWM sound circuit in the Macintosh Plus computer / 434

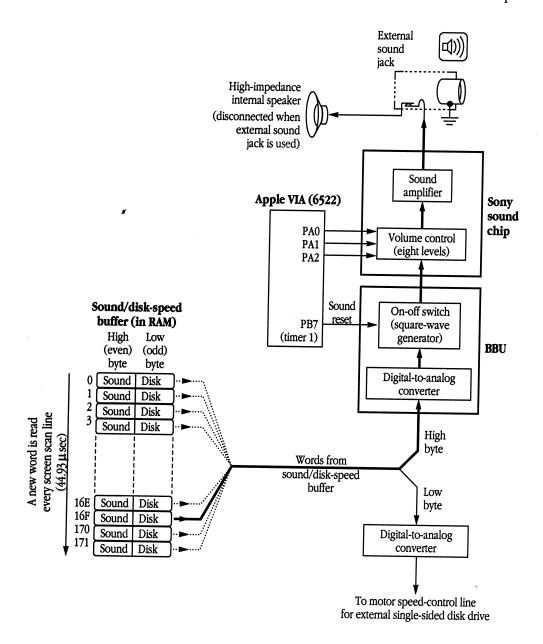

- Figure 13-4 Block diagram of the PWM sound circuit in the Macintosh SE computer / 435

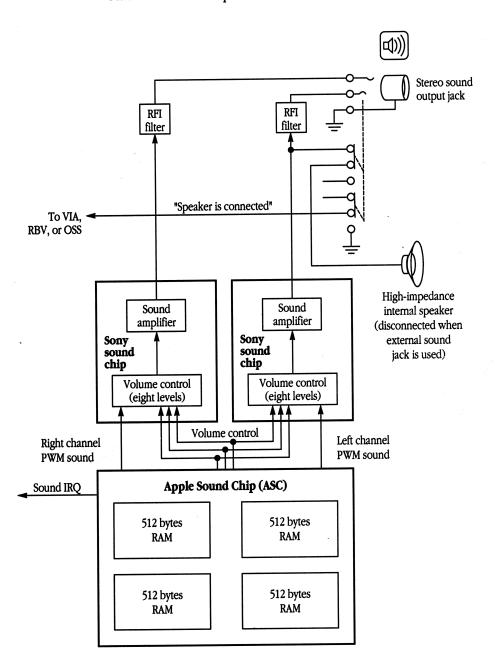

- Figure 13-5 Block diagram of the ASC sound circuit in the Macintosh Portable, Macintosh II, Macintosh IIx, Macintosh IIcx, Macintosh IIci, and Macintosh IIfx computers / 440

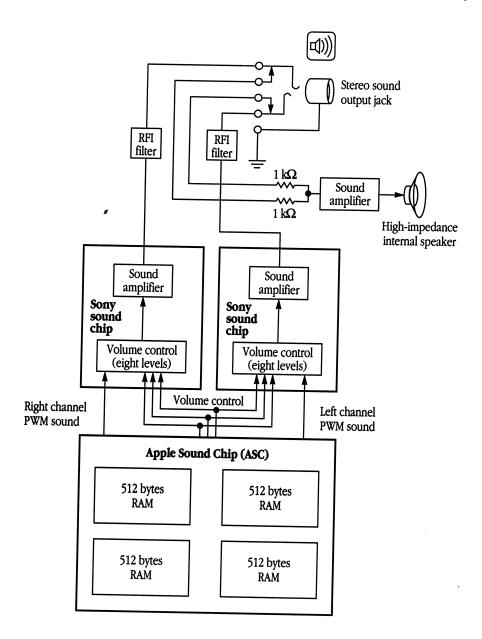

- Figure 13-6 Block diagram of the ASC sound circuit in the Macintosh SE/30 computer / 441

### Expansion Interfaces / 443

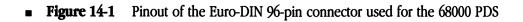

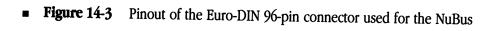

- Figure 14-1 Pinout of the Euro-DIN 96-pin connector used for the 68000 PDS / 447

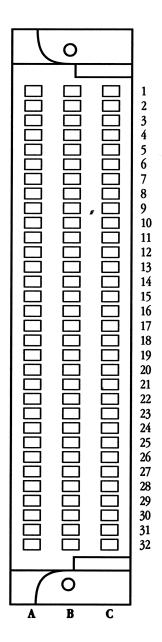

- Figure 14-2 Pinout of the Euro-DIN 120-pin connector used for the 68030 PDS / 456

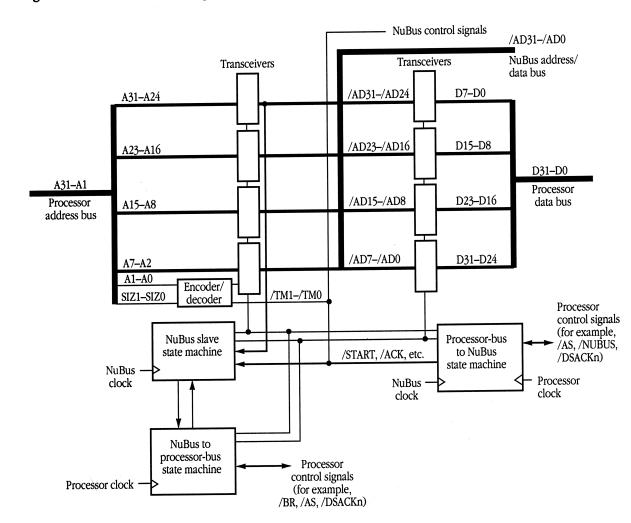

- Figure 14-3 Pinout of the Euro-DIN 96-pin connector used for the NuBus / 463

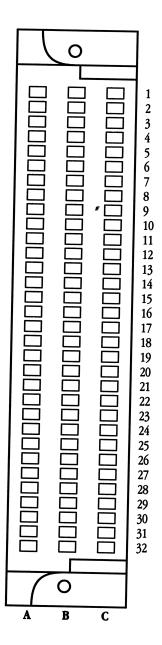

- Figure 14-4 NuBus block diagram / 466

| Table 14-1 | Signal assignments for the 68000 PDS on the              |  |

|------------|----------------------------------------------------------|--|

|            | Macintosh SE computer / 448                              |  |

| Table 14-2 | Signal descriptions for the 68000 PDS in the             |  |

|            | Macintosh SE computer / 449                              |  |

| Table 14-3 | •                                                        |  |

|            | Macintosh Portable computer / 452                        |  |

| Table 14-4 | Signal descriptions for the 68000 PDS in the             |  |

|            | Macintosh Portable computer / 453                        |  |

| Table 14-5 | Signal assignments on the 68030 PDS / 457                |  |

| Table 14-6 | Signal descriptions for the 68030 PDS:                   |  |

|            | common signals / 459                                     |  |

| Table 14-7 | Signal descriptions for the 68030 PDS:                   |  |

|            | machine-specific signals / 460                           |  |

| Table 14-8 | Signal assignments for the NuBus expansion               |  |

|            | connector / 464                                          |  |

| Table 14-9 | Signal descriptions for the NuBus expansion              |  |

|            | connector / 465                                          |  |

|            |                                                          |  |

| Macintosh  | Family Hardware Specifications / 467                     |  |

| Table A-1  | Size and weight of the Macintosh Plus computer / 469     |  |

| Table A-2  | Size and weight of the Macintosh SE computer / 471       |  |

| Table A-3  | Size and weight of the Macintosh SE/30 computer / 473    |  |

| Table A-4  | Size and weight of the Macintosh Portable computer / 475 |  |

| Table A-5  | Size and weight of the Macintosh II computer / 477       |  |

| Table A-6  | Size and weight of the Macintosh IIx computer / 480      |  |

| Table A-7  | Size and weight of the Macintosh IIcx computer / 482     |  |

| Table A-8  | Size and weight of the Macintosh IIci computer / 484     |  |

| Table A-9  | Size and weight of the Macintosh IIfx computer / 487     |  |

|            |                                                          |  |

# B Hardware-Related Global Variables / 489

A

Table B-1 Hardware-related global variables / 490

# Preface About This Book

Welcome to the Apple® *Guide to the Macintosh Family Hardware*, second edition. This book provides overviews of the architectures of Macintosh® computers and descriptions of the hardware components that make up those computers.

This book provides background and reference information for developers: hardware engineers designing peripheral devices for Macintosh computers and system programmers who need an understanding of the hardware in order to optimize their code. See the sections "Additional Reading" and "About the Macintosh Technical Documentation," later in this preface, for other books you may need.

This book is not intended to be an introduction to the basic concepts of computer hardware—you should be familiar with the terminology used in the electronics industry and with the general principles of microcomputer design and operation. Working knowledge of the Macintosh system will also be helpful.

### ▲ Warning

This book is not intended to provide information or instructions for repairing or servicing your Macintosh computer. Attempting to service or repair the computer yourself could damage the computer and will invalidate the warranty.

This preface describes the contents of this manual and the conventions used throughout the book. It also lists some other books that you might find useful, and tells you where to write or call for more information about Apple products.

### What this book contains

The following is a brief outline of the contents of this manual. See the table of contents for a complete list of the subjects covered in each chapter; see the index to find a specific topic discussed in this book.

### Organization

Guide to the Macintosh Family Hardware describes the nine Macintosh models available at the time the book was published. It also contains information about earlier Macintosh models: the Macintosh 128K, the Macintosh 512K, and the Macintosh 512K enhanced.

The nine current Macintosh models are

- Macintosh Plus

- Macintosh SE

- Macintosh SE/30

- Macintosh Portable

- Macintosh II

- Macintosh IIx

- Macintosh IIcx

- Macintosh IIci

- Macintosh IIfx

Instead of describing each model separately, this book describes each major feature for all models that have the feature. This approach has two benefits: first, it avoids unnecessary repetition of descriptions of features that are the same on different models; and second, it clarifies the differences between different models.

Each major feature in the Macintosh family is the subject of its own chapter. The major features are as follows:

- processors and control logic

- Versatile Interface Adapters (VIAs: interface ICs)

- memory organization and expansion

- power supplies and control

- keyboard and mouse on the Macintosh Plus and earlier models

- Apple Desktop Bus™ (on all models since the Macintosh Plus)

- floppy disk interfaces, two types: Apple 800 KB drive and Macintosh FDHD™ (SuperDrive™)

- serial I/O ports: similar on all models

- SCSI ports: similar on all models

- displays, three types: built-in video, expansion card video, and flat panel

- sound: two types of hardware for generating sampled sound

- expansion interfaces, two types: NuBus<sup>™</sup> and processor direct

This book has two appendixes; Appendix A lists the specifications for each model and so serves as a quick reference for readers looking for information about a particular model. Appendix B lists hardware-related global variables.

This book also contains a glossary of technical terms used in the book and an index.

### Approach

This book contains information of several different kinds, including

- specifications of internal hardware features

- explanations of important subsystems, such as the different expansion interfaces, the

Apple Desktop Bus, and the different types of displays

- detailed information needed by third-party hardware developers

- guidelines for hardware and software developers

This book provides in-depth information for certain features that are not documented elsewhere. For example, the chapter about the Apple Desktop Bus (ADB) includes more detail and more guidelines than the other chapters because this material is not available elsewhere.

Some features are not fully described in this book. Of those features, some are described in detail in other books: for example, the NuBus expansion bus is more fully described in *Designing Cards and Drivers for the Macintosh Family*, second edition. Other features are not described in detail because developers never need to deal with them: for example, the Apple custom ICs used for controlling the disk I/O port.

### Visual cues and conventions

The following visual cues are used throughout the manual to identify different types of information:

• Note: Notes like this contain interesting sidelights.

$\triangle$  Important Text set off like this contains important information that you should read before proceeding.  $\triangle$

△ **Developer tip** Boxes like this contain hints and recommendations about the best way to use the hardware. △

**Warning** Warnings like this direct your attention to something that could cause injury to the user, damage either software or hardware, or result in loss of data. ▲

When new terms are defined, they appear in **boldface.** Those terms are also defined in the glossary.

Hexadecimal numbers are preceded by a dollar sign (\$). For example, the hexadecimal equivalent of decimal number 16 is written as \$10.

Address ranges are given as *lower address through higher address* or *lower address-higher address*; in either form the range is inclusive of the given endpoints. Names of signals on a bus, on the other hand, are given as *highest-numbered signal-lowest-numbered signal*.